# **Методы высокопроизводительной цифровой обработки сигналов на основе вычислений в системе остаточных классов**

**2.3.5 – Математическое и программное обеспечение вычислительных систем, комплексов и

компьютерных сетей**

Соискатель: кандидат физико-математических наук, доцент, заведующий кафедрой математического моделирования факультета математики и компьютерных наук имени профессора Н.И. Червякова Северо-Кавказского федерального университета, заведующий отделом модульных вычислений и искусственного интеллекта регионального научно-образовательного математического центра «Северо-Кавказский центр математических исследований» Северо-Кавказского федерального университета, **Ляхов Павел Алексеевич**

Санкт-Петербург, 2026

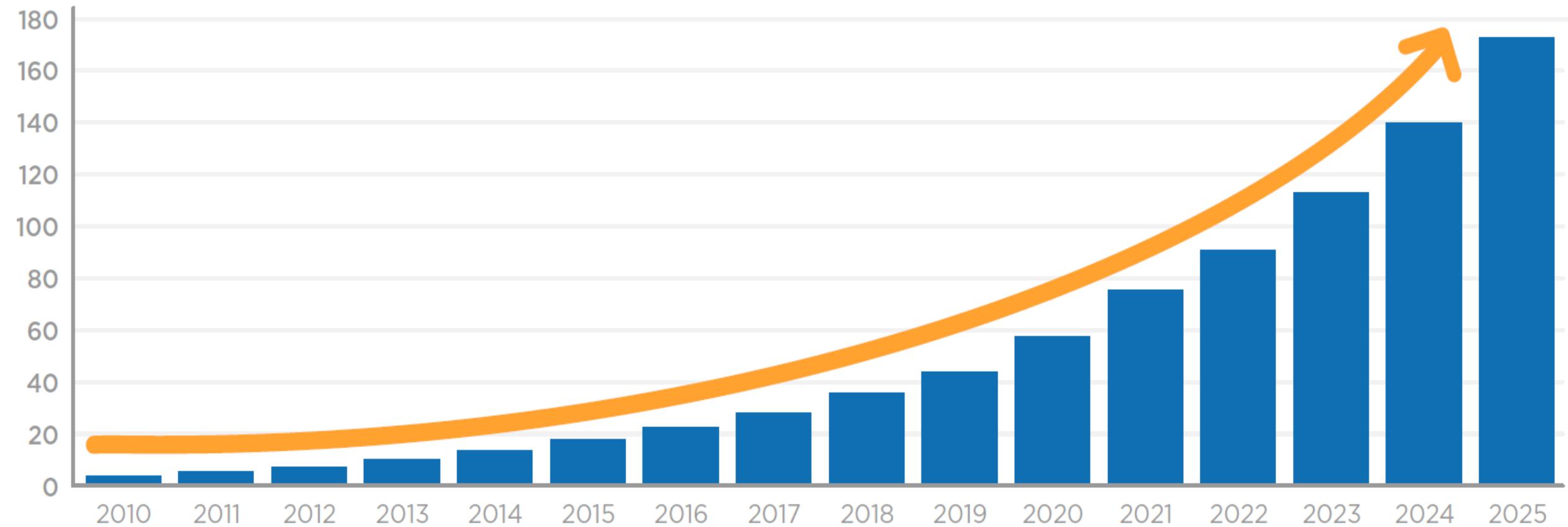

## Глобальный объем цифровых данных и темп его роста за последние 15 лет\* (зеттабайт, ЗБ)

\* Data Age 2025. The Digitization of the World From Edge to Core. URL: <https://www.seagate.com/files/www-content/our-story/trends/files/dataage-idc-report-final.pdf>

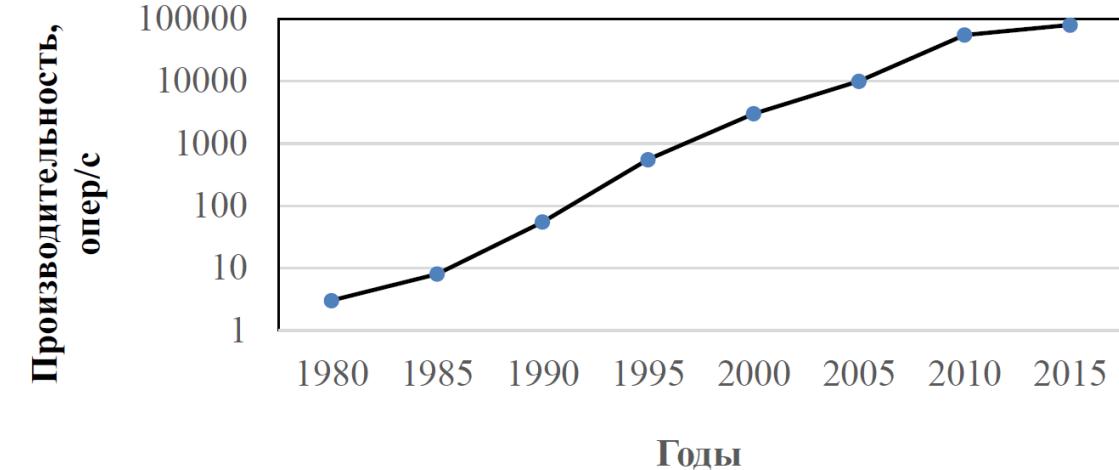

# Темп роста вычислительной мощности суперкомпьютеров\* и производительности программируемых пользователем вентильных матриц

Высокий темп непрерывного увеличения количественных и качественных характеристик цифровых сигналов, которые нужно регистрировать, обрабатывать, хранить и передавать, приводит к сильному ужесточению требований, предъявляемых к системам цифровой обработки сигналов. Современные системы, в том числе на основе искусственного интеллекта, должны обладать непомерно высокой вычислительной мощностью для удовлетворения потребности в обработке цифровых данных.

## **Противоречие в практике**

**Противоречие в практике** заключается в том, что существующие системы цифровой обработки сигналов (ЦОС), в том числе на основе искусственного интеллекта, не могут удовлетворить потребности в обработке данных, а темпы развития и совершенствования вычислительных средств и их мощности значительно уступают темпам возрастания объема цифровых одномерных и многомерных сигналов и роста вычислительной сложности методов для их обработки.

Исходя из обозначенного противоречия сформулирована **цель диссертационного исследования**, заключающаяся в повышении производительности систем ЦОС.

Достижение выбранной цели окажет большое влияние на развитие таких направлений, как медицинская визуализация, системы компьютерного зрения, робототехнические комплексы, включая беспилотный транспорт, спутниковые системы, цифровое сельское хозяйство, многочисленные приложения искусственного интеллекта.

В качестве **объекта исследования** выбраны системы ЦОС. В роли **предмета исследования** выступают методы организации параллельной обработки данных в системах ЦОС.

## Степень разработанности темы

Существует множество перспективных теоретических решений, способных повысить производительность систем ЦОС. В их число входят подходы, основанные на применении приближенных вычислений, учете неявной информационной избыточности, использовании блоков реализации арифметических операций с упрощенной структурой и многие другие.

Однако, большинство из них используют позиционные системы счисления, унаследованные от процессоров ранних поколений, что существенно ограничивает вычислительные возможности систем на их основе. Приближение к пределу миниатюризации технологических процессов производства вычислительных средств на основе кремниевых технологий требует изменения подходов к организации вычислений, особенно для использования во встраиваемых проблемно-ориентированных процессорах.

Среди различных альтернативных числовых систем, расширяющих вычислительные возможности и повышающих производительность систем цифровой обработки данных, особый интерес представляет система остаточных классов (СОК), способная обеспечить распараллеливание вычислений на арифметико-логическом уровне, что особенно эффективно при реализации модульных операций сложения, вычитания и умножения. СОК представляет собой непозиционную систему счисления, основанную на прямой сумме конечных колец, и оперирует с небольшими остатками вместо обработки чисел большой разрядности, что позволяет значительно ускорить вычисления.

## Базовые понятия системы остаточных классов

Для представления чисел в СОК и проведения вычислений используется  $n$  попарно взаимно-простых чисел  $m_i$  ( $i = 1, 2, \dots, n$ ), называемых набором модулей данной СОК. В дальнейшем будем обозначать это  $RNS = \{m_i | i = 1, 2, \dots, n\}$ . Попарная взаимная простота модулей СОК означает, что для любой пары чисел  $i$  и  $j$ , удовлетворяющей условиям  $1 \leq i < j \leq n$ , выполняется условие  $\text{GCD}(m_i, m_j) = 1$ , где  $\text{GCD}(x, y)$  обозначает наибольший общий делитель чисел  $x$  и  $y$ .

Динамический диапазон  $M$  данных, представимых в СОК, определяется по формуле  $M = \prod_{i=1}^n m_i$ . Из теории чисел известно, что любая система сравнений относительно  $X$ :

$$\begin{cases} X \equiv x_1 \pmod{m_1}, \\ X \equiv x_2 \pmod{m_2}, \\ \dots \\ X \equiv x_n \pmod{m_n}, \end{cases}$$

имеет единственное решение на подмножестве целых чисел  $\{0, 1, \dots, M - 1\}$ , что означает возможность взаимно-однозначного отображения указанного множества на множество кортежей  $\{x_1, x_2, \dots, x_n\}$ , где  $0 \leq x_i < m_i$  для  $i = 1, 2, \dots, n$ . Данный факт носит название Китайской теоремы об остатках и открывает возможность машинного представления целочисленного типа данных без знака в виде совокупности чисел  $\{x_1, x_2, \dots, x_n\}$ , ограниченных вычислительным диапазоном системы. Для знакового представления чисел в СОК динамический диапазон  $M$  делится на две части, при этом поддерживается представление чисел  $X$ , удовлетворяющих одному из требований:

$$-\frac{M-1}{2} \leq X \leq \frac{M-1}{2} \text{ для нечетных } M \text{ и } -\frac{M}{2} \leq X \leq \frac{M}{2} - 1 \text{ для четных } M.$$

## Демонстрация арифметического параллелизма системы остаточных классов

$$A = 23, \quad B = 37, \quad C = 398$$

$$RNS = \{7, 15, 16\} \quad M = 7 \cdot 15 \cdot 16 = 1680$$

$$A = (2, 8, 7), \quad B = (2, 7, 5), \quad C = (6, 8, 14)$$

$$A \cdot B + C$$

Вычисления в позиционной системе счисления

$$\begin{array}{r} \times \quad 23 \\ \times \quad 37 \\ \hline 851 \end{array} \qquad \begin{array}{r} + \quad 851 \\ + \quad 398 \\ \hline 1249 \end{array}$$

Вычисления в системе остаточных классов

$$\begin{array}{r} \times \quad (2, 8, 7) \\ \times \quad (2, 7, 5) \\ \hline (4, 11, 3) \end{array} \qquad \begin{array}{r} + \quad (4, 11, 3) \\ + \quad (6, 8, 14) \\ \hline (3, 4, 1) \end{array}$$

Проверка

$$1249 \bmod 7 = 3$$

$$1249 \bmod 15 = 4$$

$$1249 \bmod 16 = 1$$

# Параллельная обработка данных в системе остаточных классов

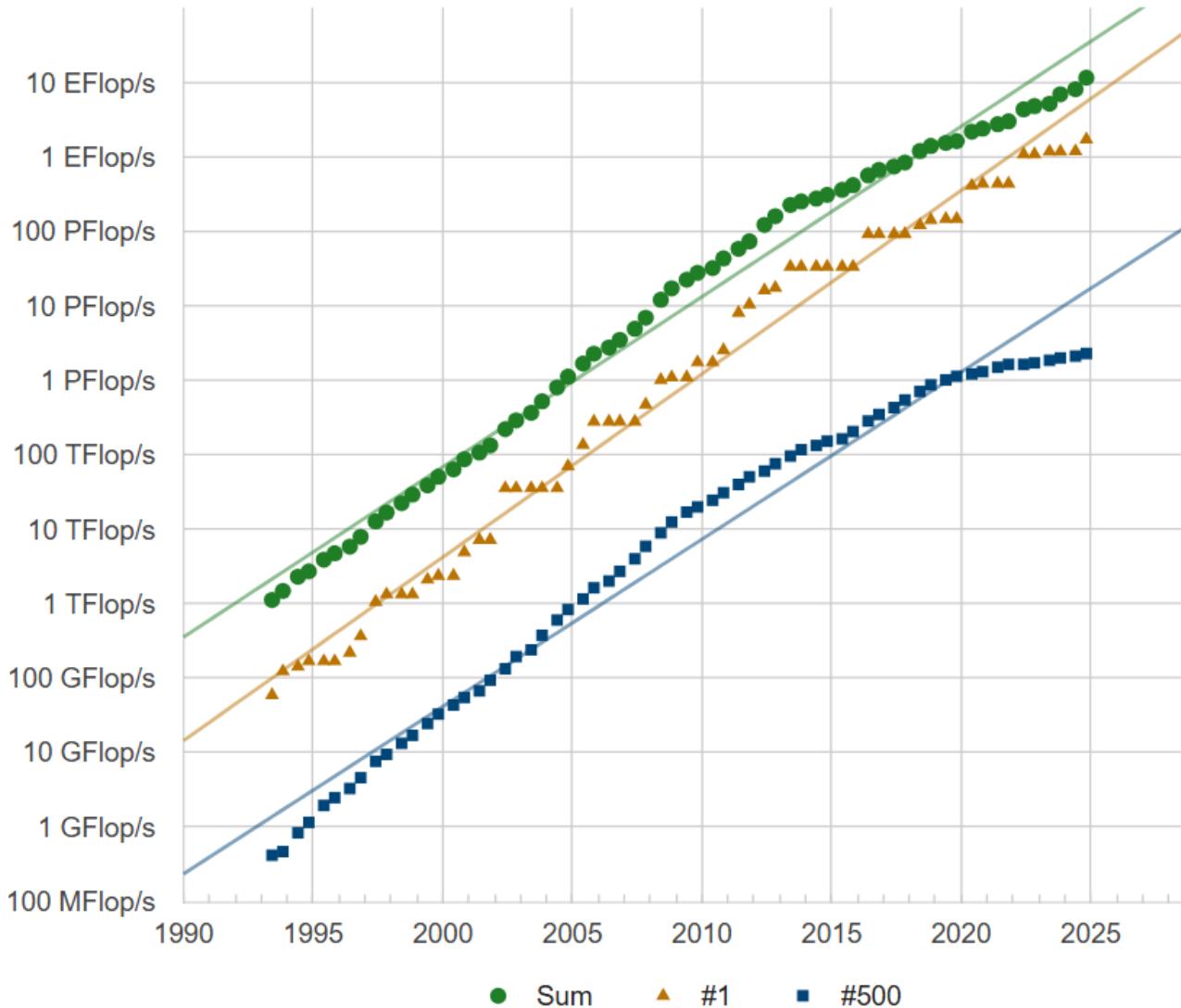

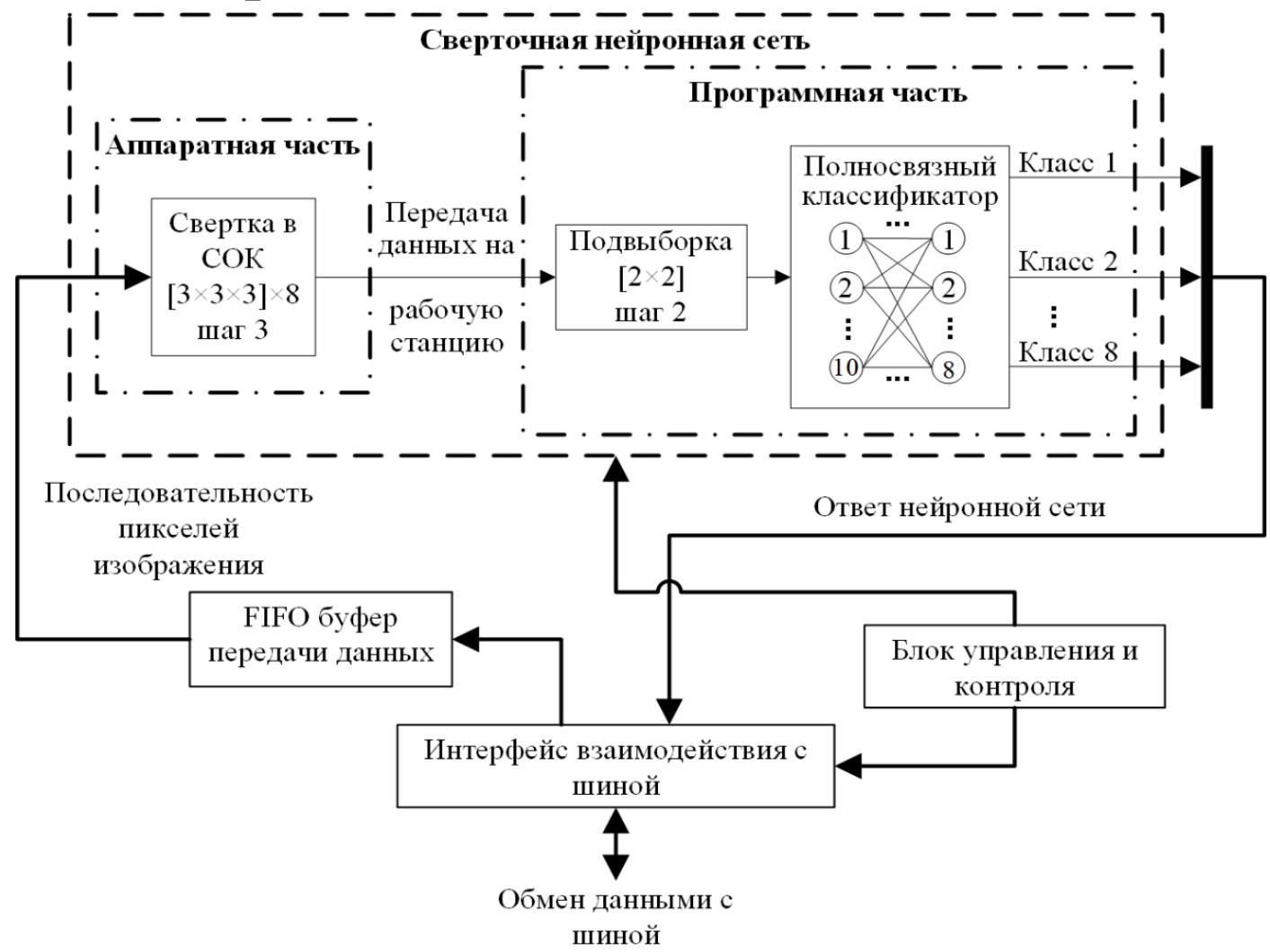

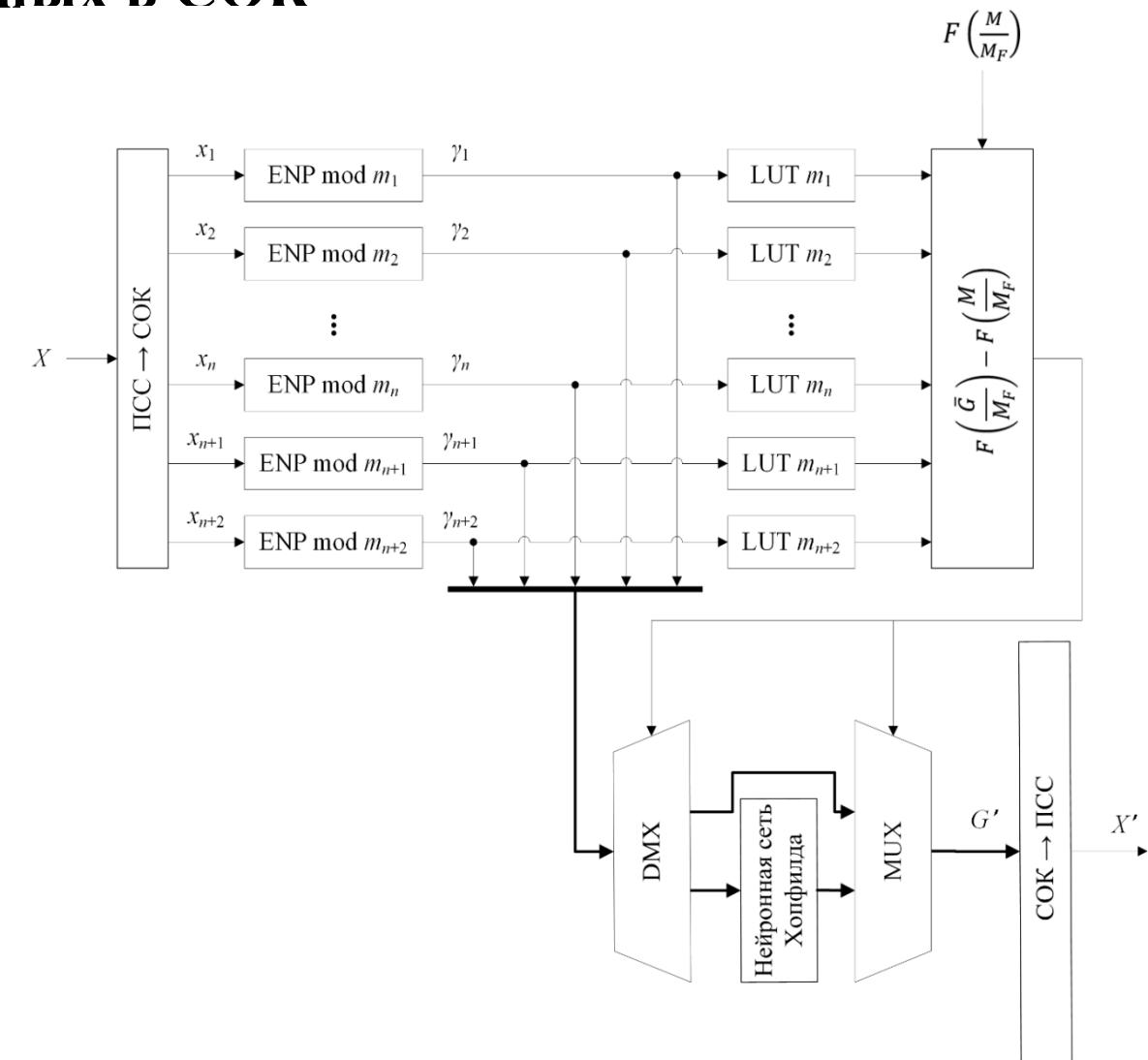

При параллельной обработке данных в СОК, согласно представленной схеме, на вход подается информация, представленная в позиционной системе счисления (ПСС). Устройство прямого преобразования ПСС→СОК вычисляет представление поступивших данных в СОК, т. е. генерирует кортежи  $\{x_1, x_2, \dots, x_n\}$  для каждого поступившего на вход числа  $X$  по формуле  $x_i \equiv |X|_{m_i}$  для  $i = 1, 2, \dots, n$ . После выполнения прямого преобразования ПСС→СОК в арифметических каналах по каждому из модулей  $\{m_1, m_2, \dots, m_n\}$  выполняются модульные операции сложения, вычитания и умножения, причем в силу теоретико-числовых свойств, это выполняется параллельно, т.е. результаты вычислений в каждом из арифметических каналов не учитываются в других. На практике это означает, что обработка данных при использовании набора модулей  $\{m_1, m_2, \dots, m_n\}$ , имеющему небольшую разрядность по сравнению с разрядностью диапазона  $M$ , выполняется за счет параллельной организации вычислений быстрее, чем аналогичные арифметические операции в ПСС с диапазоном  $M$ . Устройство обратного преобразования позволяет восстановить позиционное представление данных. Оно может быть

реализовано по формуле  $X = \left| \sum_{i=1}^n \left( |M_i^{-1}|_{m_i} M_i \right) x_i \right|_M$ , где  $M_i = \frac{M}{m_i}$ , а

выражение  $|M_i^{-1}|_{m_i}$  означает обратный элемент для  $M_i$  в мультиPLICативной группе кольца вычетов по модулю  $m_i$ .

# Обработка данных в системе остаточных классов с немодульными операциями

Указанную схему можно усовершенствовать, добавив элементы обеспечения отказоустойчивости. Отказоустойчивые свойства СОК проявляются при добавлении к модулям  $\{m_1, m_2, \dots, m_n\}$  множества избыточных модулей  $\{m_{n+1}, m_{n+2}, \dots, m_{n+r}\}$ . СОК, множество модулей которой  $\{m_1, \dots, m_n, m_{n+1}, \dots, m_{n+r}\}$  разделено на информационные ( $m_i$ ,  $1 \leq i \leq n$ ) и избыточные ( $m_i$ ,  $n+1 \leq i \leq r$ ) называется избыточной системой остаточных классов (ИСОК). В ИСОК диапазон, вычисляемый по формуле  $M_F = \prod_{i=1}^{n+r} m_i$ , является

полным диапазоном ИСОК. Прямое преобразование ПСС $\rightarrow$ ИСОК отличается от прямого преобразования ПСС $\rightarrow$ СОК необходимостью вычисления остатков как по информационным, так и по избыточным модулям системы по формуле  $x_i \equiv |X|_{m_i}$  для  $i = 1, 2, \dots, n + r$ . Арифметические каналы разделены на обычные, соответствующие информационным модулям ИСОК, и избыточные, соответствующие избыточным модулям ИСОК. Обратный преобразователь ИСОК $\rightarrow$ ПСС отличается от обратного преобразователя СОК $\rightarrow$ ПСС вычислениями по полному диапазону

$$\text{системы } M_F \text{ по формуле } X = \left| \sum_{i=1}^{n+r} \left( |M_i^{-1}|_{m_i} M_i \right) x_i \right|_{M_F}.$$

## Противоречие в науке

Несмотря на высокий потенциал в повышении производительности систем ЦОС, организация обработки данных в СОК накладывает множество ограничений, в том числе на вычислительный диапазон, и снижает эффективность реализации немодульных операций, что значительно усложняет возможность ее широкого практического применения для решения ряда прикладных задач ЦОС.

Требуется развитие методологии применения СОК для эффективной по скорости вычислений реализации арифметических операций с организацией модульных вычислений при обработке многомерных сигналов. Помимо этого, необходимо разработать подходы к ЦОС, основанные на комбинированном применении методов организации арифметической обработки данных в СОК и иных решений, сочетающихся с СОК и позволяющих значимо усилить ее преимущества и в значительной степени нивелировать ее недостатки.

Таким образом, имеет место следующее **противоречие в науке**: несмотря на наличие развитой теории вычислений в СОК, отсутствует методологический аппарат для создания технологии высокопроизводительной ЦОС с вычислениями в СОК. Для разрешения данного противоречия обозначена **научная проблема**: необходимость разработки методов параллельной обработки данных в СОК для создания технологии высокопроизводительной ЦОС.

## **Частные задачи диссертационного исследования**

1. Аналитический обзор современных проблем и подходов к улучшению эксплуатационных характеристик систем цифровой обработки сигналов.

2. Разработка обобщенной модели усовершенствованной цифровой обработки сигналов в системе остаточных классов.

3. Разработка архитектуры цифрового фильтра для параллельной обработки сигналов в системе остаточных классов.

4. Разработка метода высокоскоростной фильтрации цифровых изображений на основе блочной обработки данных.

5. Разработка методов и архитектур для обработки данных, представленных в системе остаточных классов, при выполнении немодульных операций.

6. Разработка метода и алгоритма вейвлет-обработки сигналов с вычислениями в системе остаточных классов.

7. Разработка технологии создания систем высокопроизводительной цифровой обработки сигналов на основе вычислений в системе остаточных классов.

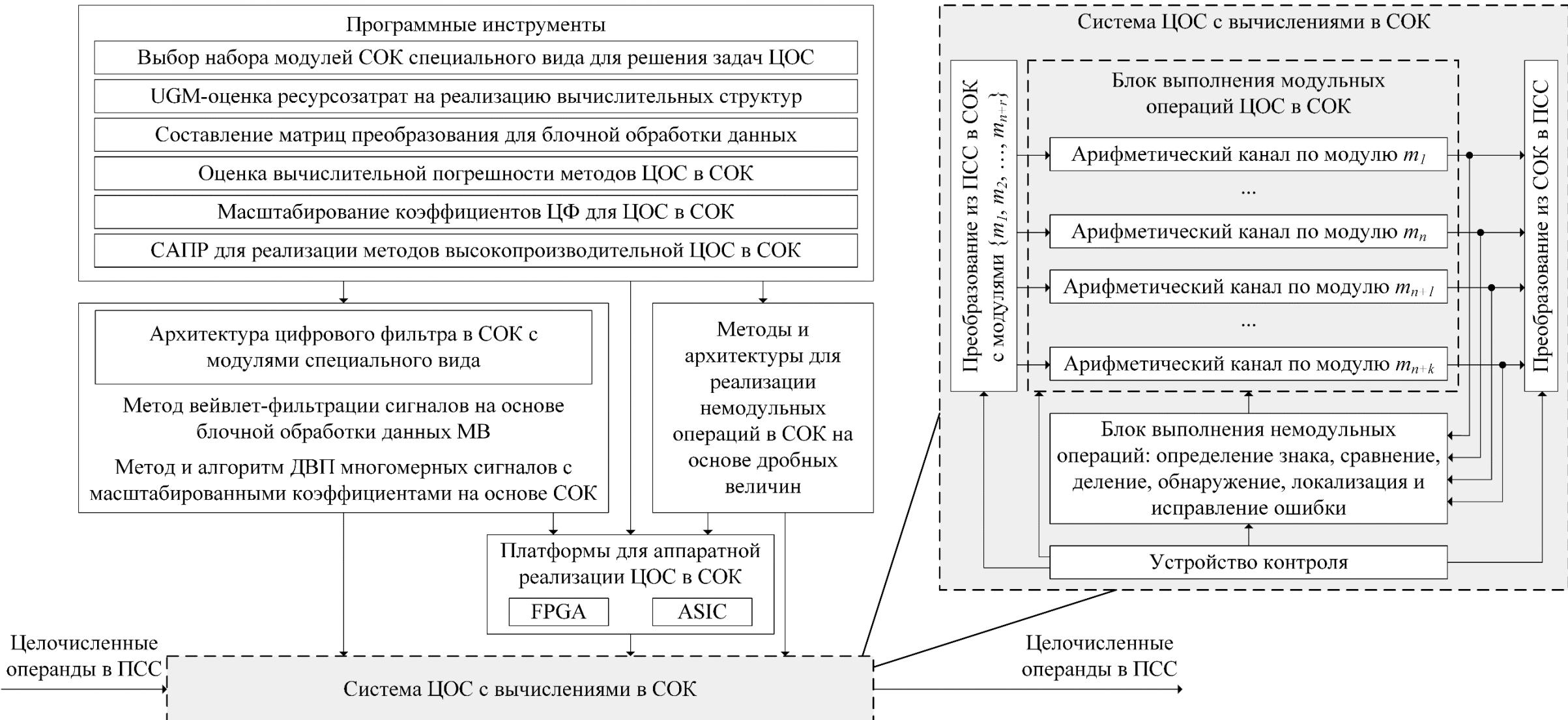

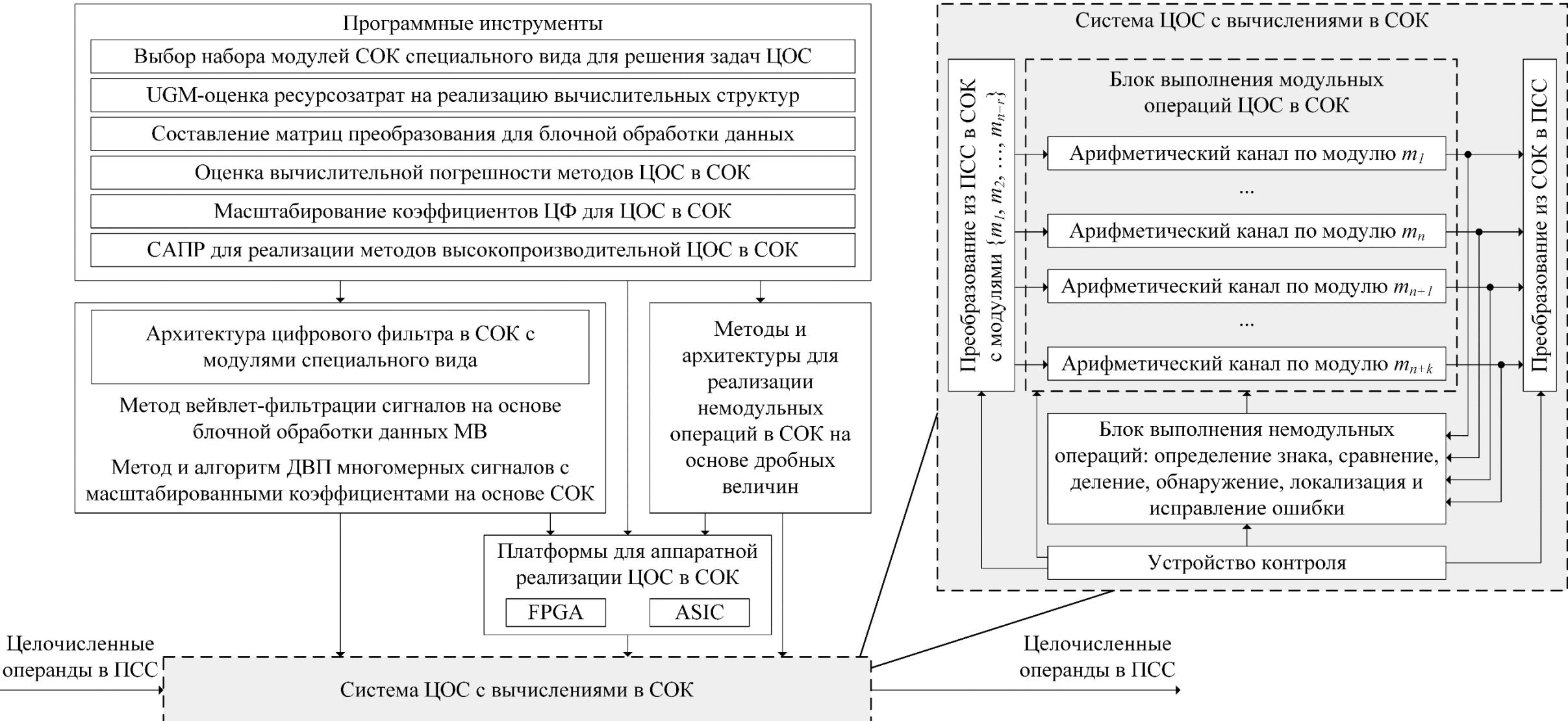

# Графическая иллюстрация разработанной обобщенной модели

**Положение 1. Обобщенная модель усовершенствованной цифровой обработки сигналов в системе остаточных классов, обеспечивающая повышение производительности за счет системного объединения параллельной модульной арифметики, блочной обработки данных, методов выполнения немодульных операций на основе дробных величин и масштабирования коэффициентов фильтров**

## **Описание иллюстрации разработанной обобщенной модели**

Графическая иллюстрация обобщенной модели представлена демонстрирует расширение методологии ЦОС посредством использования различных инструментов и принципов их взаимодействия друг с другом. Важно отметить, что помимо значимых разработок, а именно архитектуры цифрового фильтра для параллельной обработки сигналов в СОК (раздел 2.3), метода высокоскоростной вейвлет-фильтрации сигналов на основе блочной обработки данных с уменьшением количества используемых умножений (раздел 3.4), методов и архитектур для реализации немодульных операций в СОК и преобразования данных, в частности метода и архитектуры для обратного преобразования чисел из модулярного кода в позиционный (подраздел 4.1.2), метода определения знака числа в СОК (раздел 4.2), метода и архитектуры для сравнения чисел в СОК (раздел 4.3) и метода и архитектуры для обнаружения, локализации и исправления ошибок в СОК (подраздел 4.4.2), алгоритма масштабирования коэффициентов вейвлет-фильтров (подраздел 5.2.1) и метода вейвлет-обработки цифровых сигналов с использованием масштабированных коэффициентов и модулярных вычислений (5.2.2), также важное место занимают различные программные инструменты для выбора эффективных по ресурсозатратам наборов модулей СОК (разделы 2.1 и 2.2) на основе предварительной теоретической оценки вычислительных структур в ПСС и СОК на основе UGM (разделы 2.2-2.4, 3.2 и 3.3), составления вспомогательных матриц преобразования (раздел 3.1), оценки погрешности вычислений на разных этапах обработки данных (разделы 5.1 и 5.2), преобразования коэффициентов используемых ЦФ (разделы 5.1 и 5.2). Отдельно следует выделить важность САПР, способных осуществить эффективную по ресурсозатратам аппаратную реализацию различных методов ЦОС в СОК на современных платформах, в частности FPGA и ASIC.

**Положение 1. Обобщенная модель усовершенствованной цифровой обработки сигналов в системе остаточных классов, обеспечивающая повышение производительности за счет системного объединения параллельной модулярной арифметики, блочной обработки данных, методов выполнения немодульных операций на основе дробных величин и масштабирования коэффициентов фильтров**

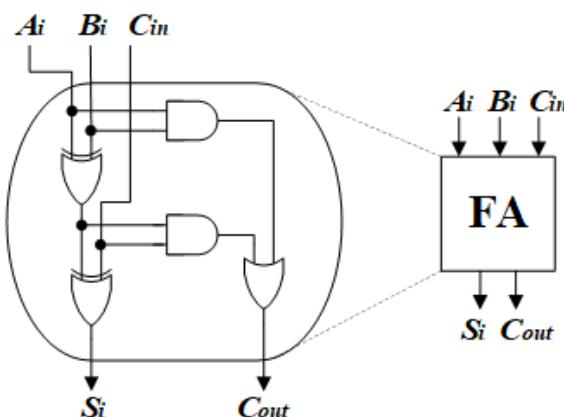

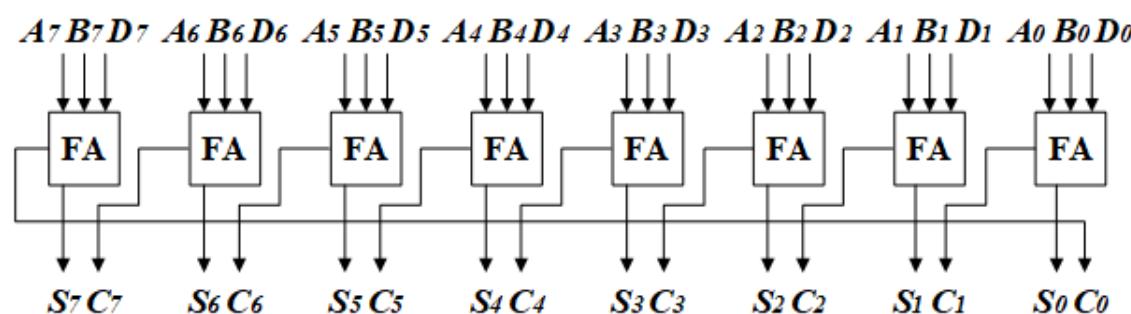

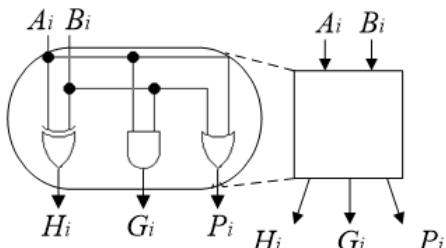

## Логические схемы сумматоров на примере сложения 8-битных чисел

Логическая схема полного сумматора

(full adder, FA)

Логическая схема 8-битного сумматора с последовательным переносом (carry propagate adder, CPA)

Логическая схема 8-битного сумматора с сохранением переноса (carry save adder, CSA)

Логическая схема сумматора по модулю  $2^8-1$  с сохранением переноса (carry save modulo adder, CSMA)

Положение 2. Архитектура цифрового фильтра в системе остаточных классов с модулями специального вида, реализующая ключевой вычислительный элемент обобщенной модели и обеспечивающая параллельную обработку сигналов

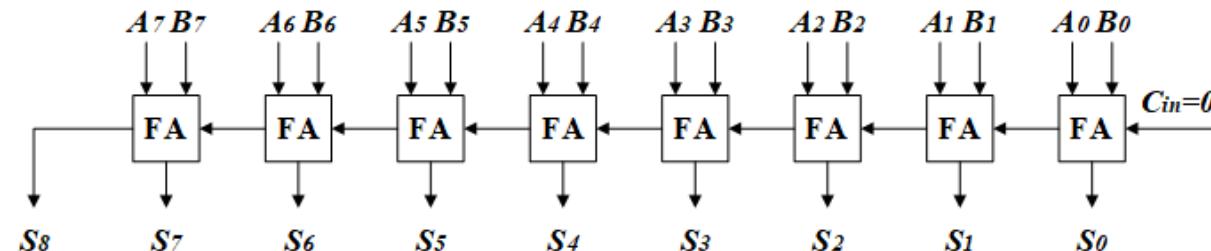

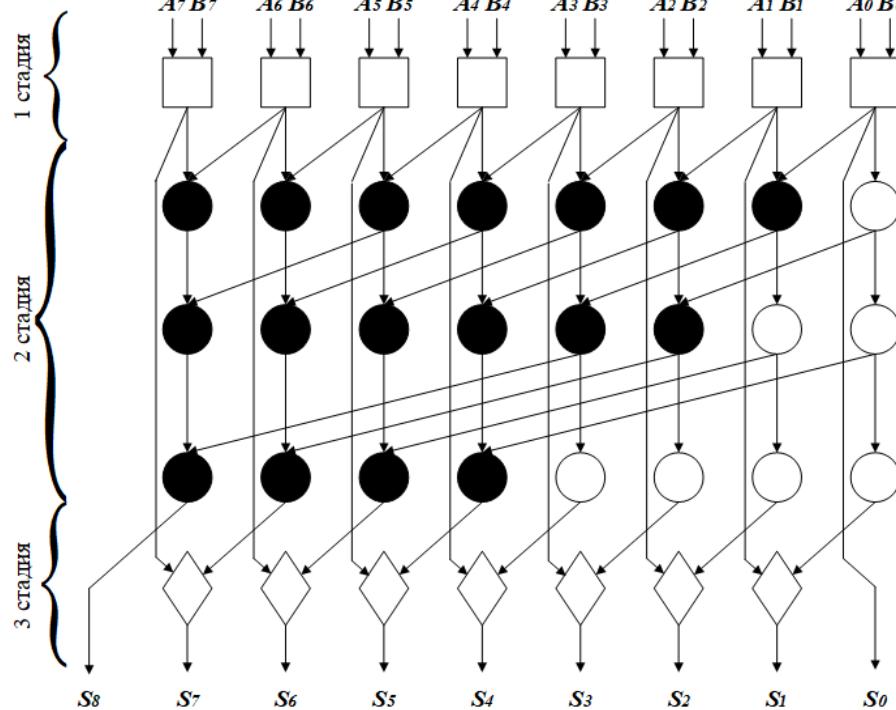

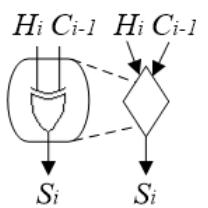

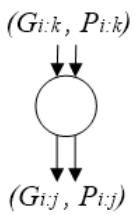

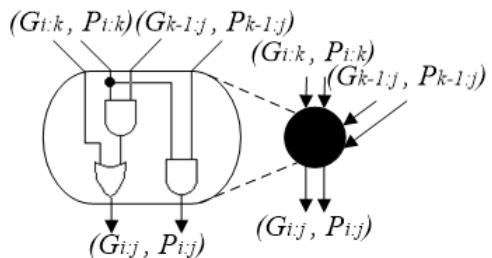

# Логические схемы параллельно-префиксных сумматоров

Логические схемы базовых блоков параллельно-префиксного сумматора

Логическая схема 8-битного параллельно-префиксного сумматора Когге-Стоуна (Kogge-Stone adder, KSA)

Логическая схема сумматора Когге-Стоуна для сложения чисел по модулю  $2^8 - 1$  (Kogge-Stone modulo adder, KSMA)

Положение 2. Архитектура цифрового фильтра в системе остаточных классов с модулями специального вида, реализующая ключевой вычислительный элемент обобщенной модели и обеспечивающая параллельную обработку сигналов

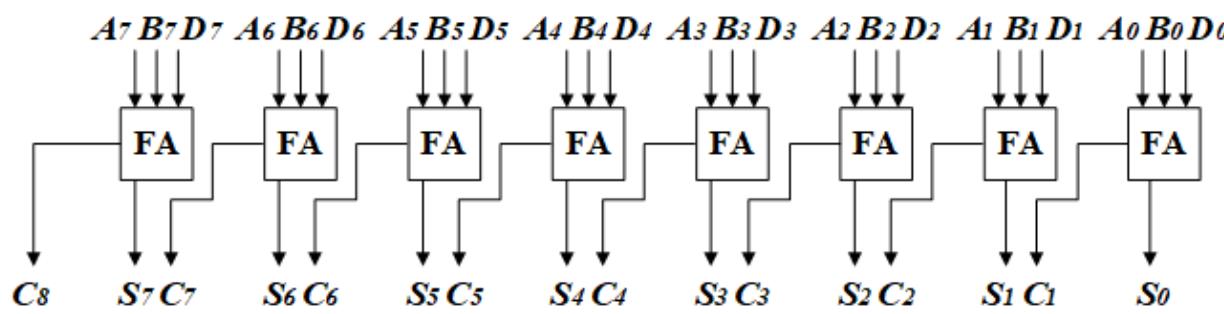

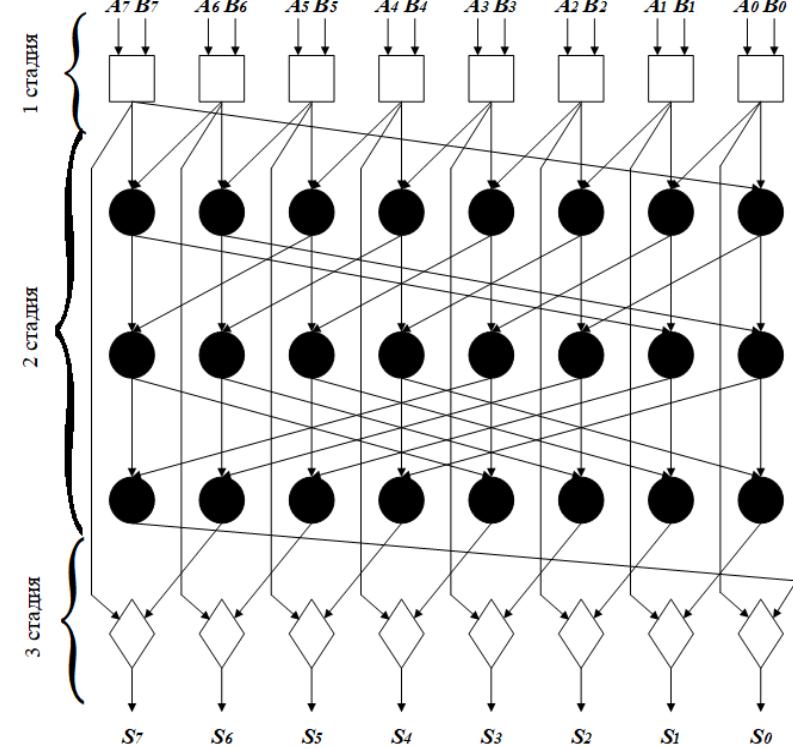

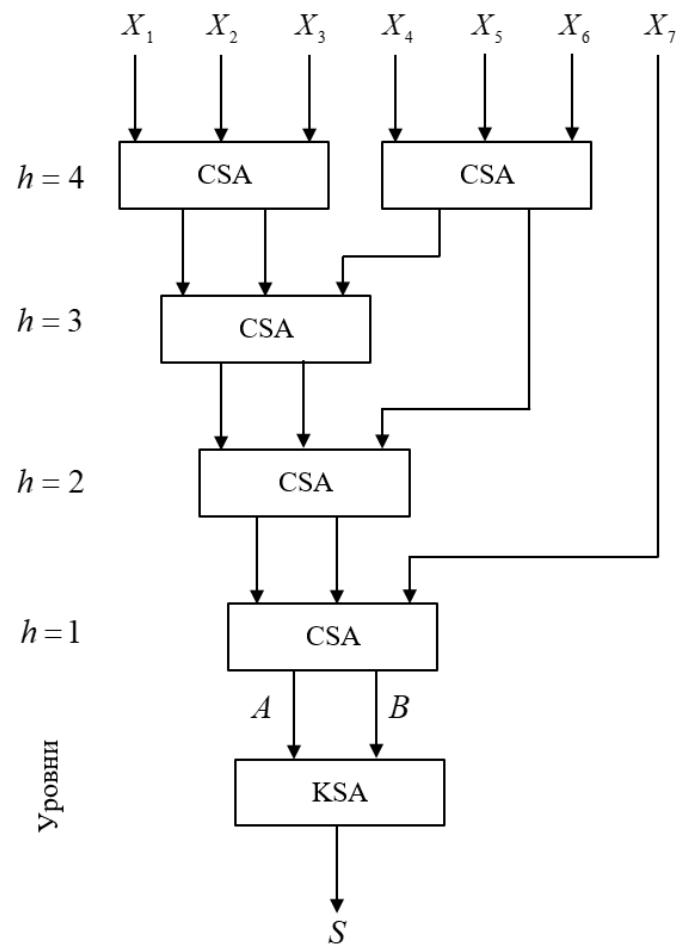

# Логические схемы многовходовых сумматоров и умножителя

Логическая схема устройства для быстрого суммирования 7 слагаемых

Логическая схема умножителя двух чисел

(general multiplier, GM)

Логическая схема устройства для быстрого суммирования 7 слагаемых по модулю  $2^k - 1$

## Теоретическая оценка ресурсозатрат с использованием unit-gate model (UGM)

В данной модели задержка и площадь двухходовых логических вентилей AND или OR считаются единицей измерения задержки и площади средства вычислительной техники, соответственно. Логический вентиль NOT считается как ноль при подсчете задержки и площади устройства. Логические вентили XOR и XNOR считаются за две единицы как при подсчете задержки, так и при подсчете площади. Если обозначить рассчитанную по указанной модели задержку, как  $U_{delay}$ , а площадь, как  $U_{area}$ , то для перечисленных логических вентилей будем иметь следующее описание:

$$U_{delay}(NOT) = 0, U_{area}(NOT) = 0, U_{delay}(AND) = 1, U_{area}(AND) = 1, U_{delay}(OR) = 1, U_{area}(OR) = 1,$$

$$U_{delay}(XOR) = 2, U_{area}(XOR) = 2, U_{delay}(XNOR) = 2, U_{area}(XNOR) = 2.$$

Площадь более сложных средств вычислительной техники рассчитывается как сумма площадей всех логических элементов, входящих в них. Задержка более сложных средств вычислительной техники рассчитывается как сумма задержек логических элементов самого длинного пути от входа до выхода системы. Недостатком данной модели является игнорирование эффектов нагрузочной способности выходов, как отдельных логических элементов, так и микросхемы в целом, что требует верификации теоретических результатов при помощи аппаратной реализации на современных платформах. Однако, в качестве приближенной теоретической оценки ожидаемых ресурсозатрат на реализацию вычислительных алгоритмов данная модель показывает хорошие практические результаты.

# Теоретическая оценка ресурсозатрат на реализацию параллельной обработки данных в позиционной системе счисления и в СОК

Ресурсозатраты на реализацию вычислений в позиционной системе счисления

| Устройство | Задержка                      |               | Площадь                        |                 |

|------------|-------------------------------|---------------|--------------------------------|-----------------|

|            | $U_{delay}$                   | Сложность     | $U_{area}$                     | Сложность       |

| CPA        | $4k$                          | $O(k)$        | $7k$                           | $O(k)$          |

| CSA        | 4                             | $O(1)$        | $7k$                           | $O(k)$          |

| KSA        | $2\log_2 k + 4$               | $O(\log_2 k)$ | $3k \log_2 k + 3k + 1$         | $O(k \log_2 k)$ |

| МОА        | $6,8\log_2 N + 2\log_2 k + 4$ | $O(\log_2 k)$ | $3k \log_2 k + 7kN - 11k + 1$  | $O(k^2)$        |

| CM         | $8,8\log_2 k + 4$             | $O(\log_2 k)$ | $3k \log_2 k + 7k^2 - 11k + 1$ | $O(k^2)$        |

| GM         | $8,8\log_2 k + 5$             | $O(\log_2 k)$ | $3k \log_2 k + 8k^2 - 11k + 1$ | $O(k^2)$        |

Ресурсозатраты на реализацию вычислений в СОК по модулю  $2^k - 1$

| Устройство | Задержка                      |               | Площадь                   |                 |

|------------|-------------------------------|---------------|---------------------------|-----------------|

|            | $U_{delay}$                   | Сложность     | $U_{area}$                | Сложность       |

| EAC-CPA    | $8k$                          | $O(k)$        | $14k$                     | $O(k)$          |

| EAC-CSA    | 4                             | $O(1)$        | $7k$                      | $O(k)$          |

| EAC-KSA    | $2\log_2 k + 4$               | $O(\log_2 k)$ | $3k \log_2 k + 6k$        | $O(k \log_2 k)$ |

| MOMA       | $6,8\log_2 N + 2\log_2 k + 4$ | $O(\log_2 k)$ | $3k \log_2 k + 7kN - 8k$  | $O(k^2)$        |

| CMM        | $8,8\log_2 k + 4$             | $O(\log_2 k)$ | $3k \log_2 k + 7k^2 - 8k$ | $O(k^2)$        |

| GMM        | $8,8\log_2 k + 5$             | $O(\log_2 k)$ | $3k \log_2 k + 8k^2 - 8k$ | $O(k^2)$        |

Сопоставление результатов из представленных таблиц позволяет сделать важный вывод о том, что задержка однотипных систем (кроме CPA) для сложения и умножения чисел в позиционной системе счисления (ПСС) и в СОК по модулю  $2^k - 1$  совпадает, а аппаратные затраты для соответствующих систем в остаются на одном уровне сложности. Данный факт делает весьма выгодным использование модулей вида  $2^k - 1$  в СОК, так как такие модули принципиально не усложняют арифметические системы, в то время как разрядность модулей СОК обычно существенно меньше (не менее чем в три раза) разрядности соответствующего диапазона в ПСС.

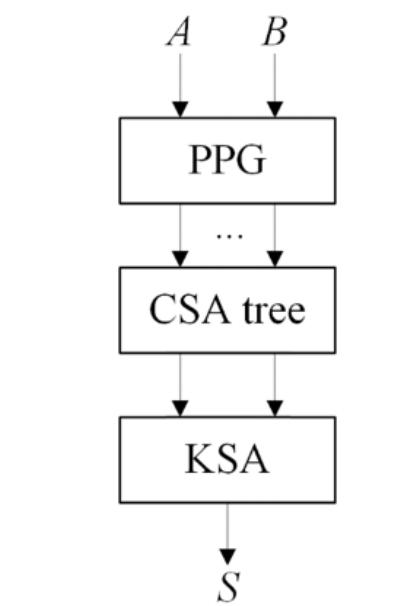

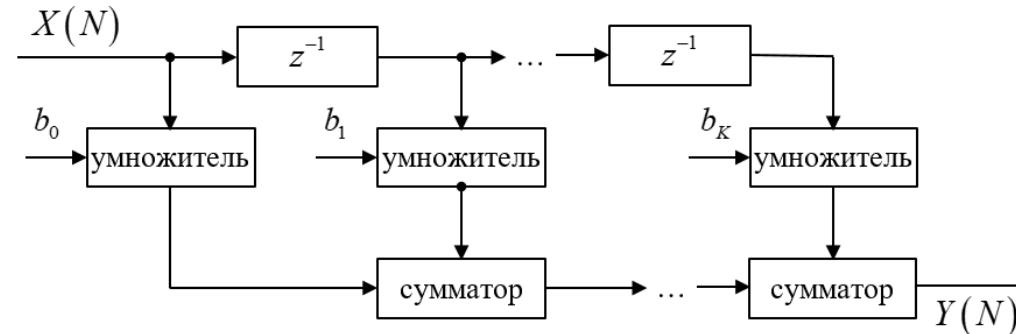

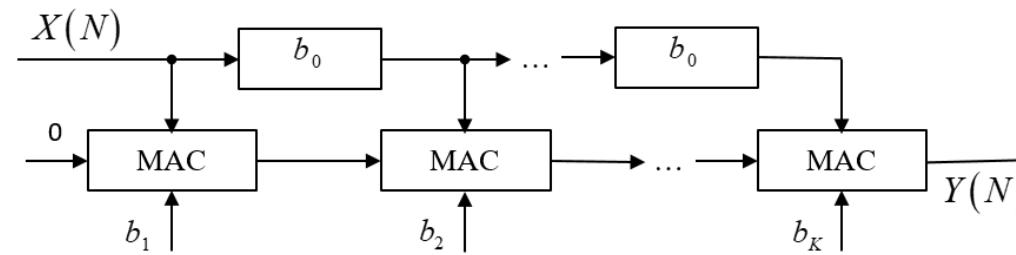

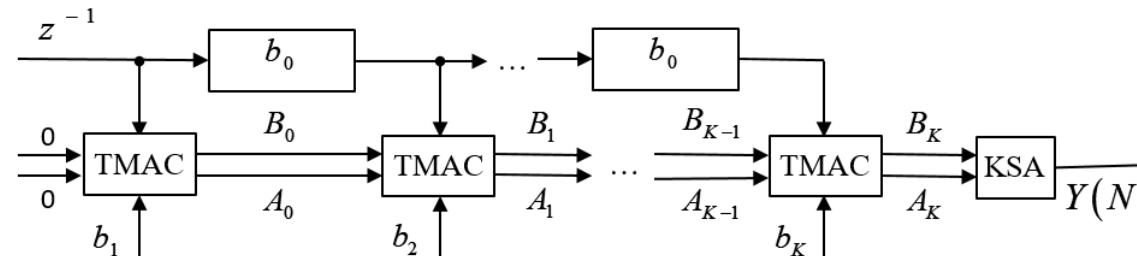

# Схемы цифровых фильтров с конечной импульсной характеристикой

Схема блока умножения с накоплением (multiply-accumulate unit, MAC unit)

A

B

KSA

Y<sub>i</sub>

Схема усеченного блока умножения с накоплением (truncated multiply-accumulate unit, TMAC unit)

A<sub>i</sub>

B<sub>i</sub>

Схема КИХ-ЦФ порядка K

Схема КИХ-ЦФ порядка K на основе MAC-блоков

Схема КИХ-ЦФ порядка K на основе TMAC-блоков

Положение 2. Архитектура цифрового фильтра в системе остаточных классов с модулями специального вида, реализующая ключевой вычислительный элемент обобщенной модели и обеспечивающая параллельную обработку сигналов

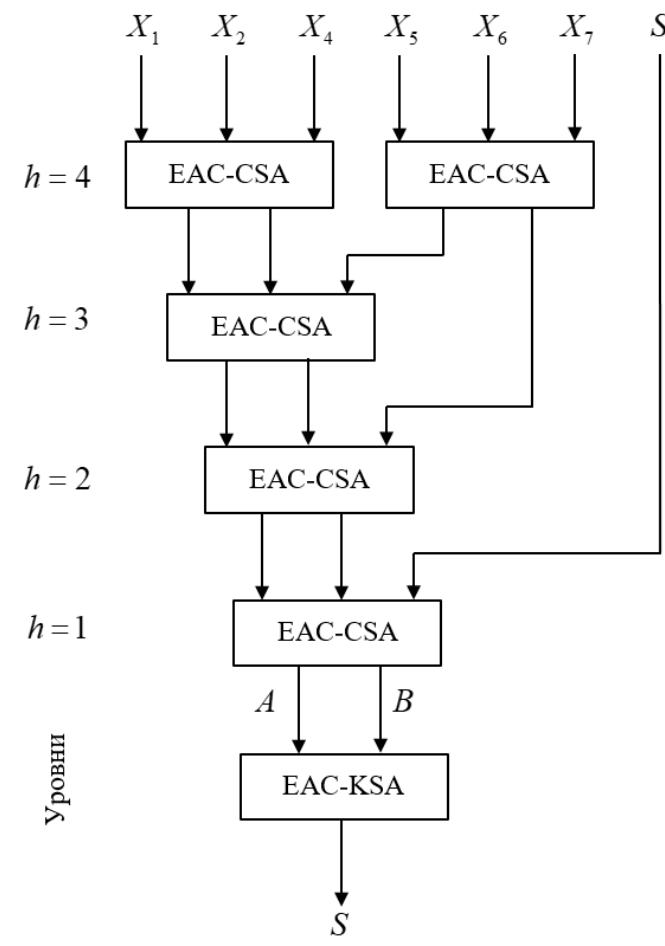

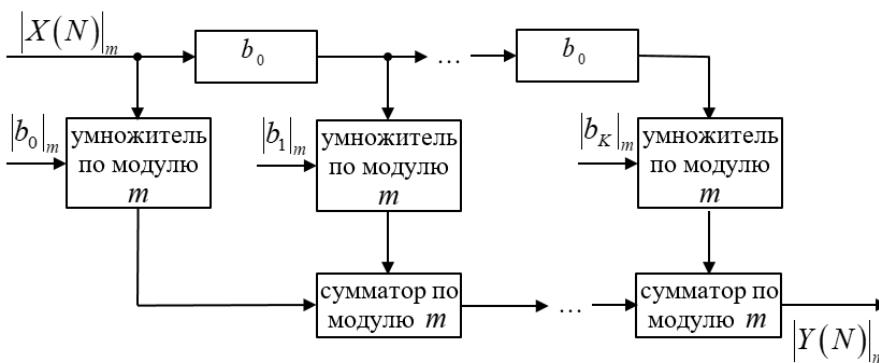

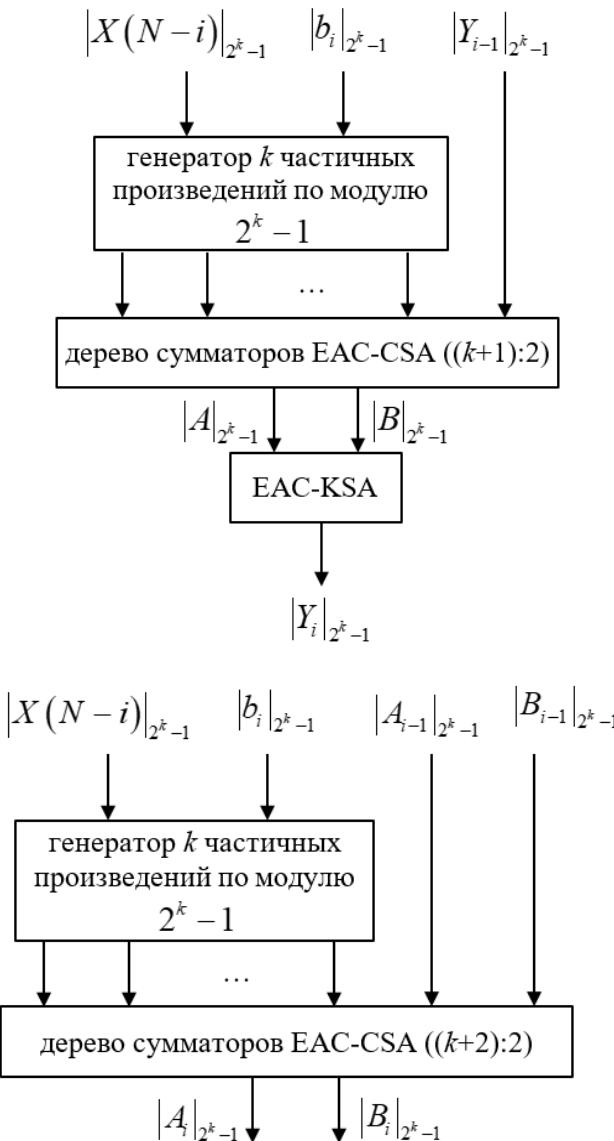

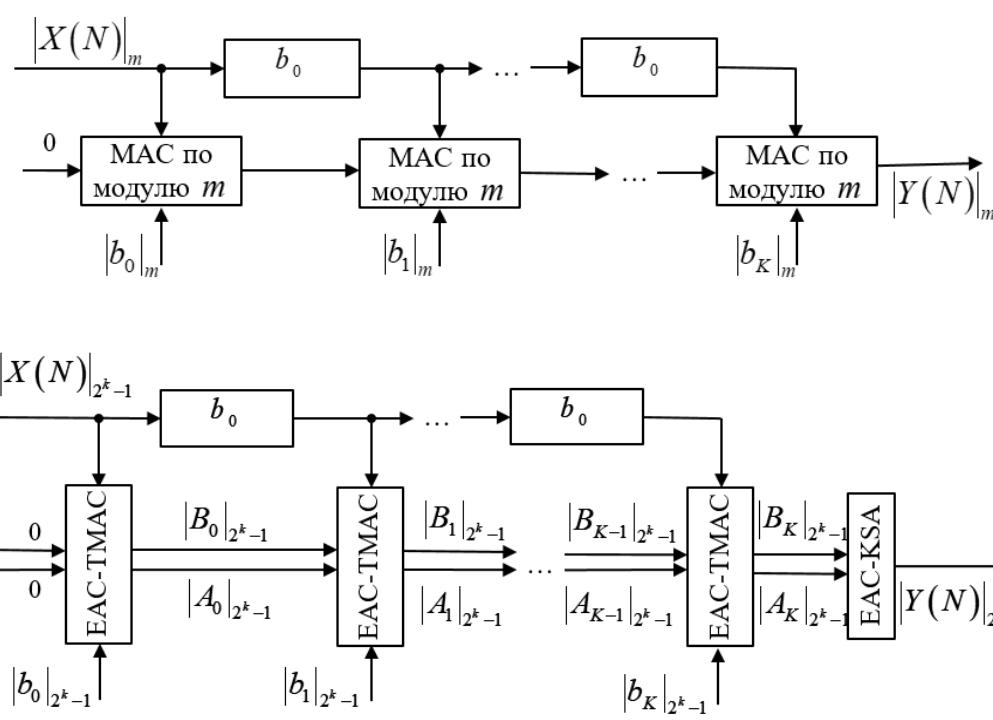

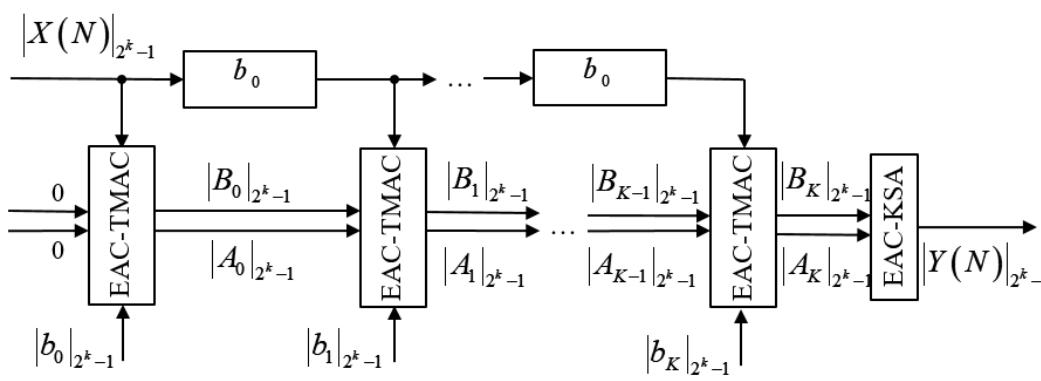

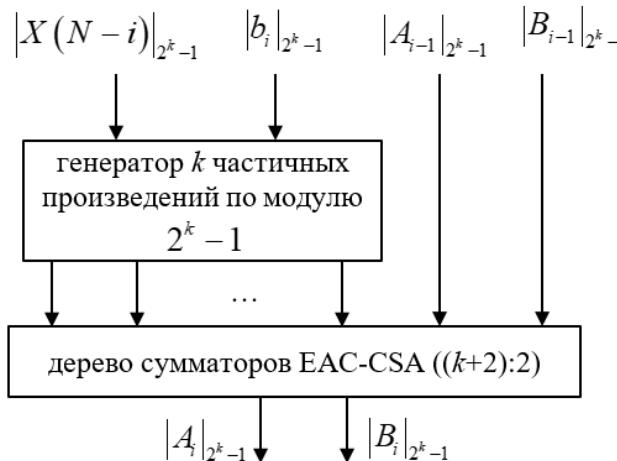

# Схемы цифровых фильтров с конечной импульсной характеристикой в СОК

Схема блока ЕАС-МАС

по модулю  $2^{k-1}$

Схема КИХ-ЦФ

порядка  $K$  по

модулю  $m$

Схема КИХ-ЦФ

порядка  $K$  на основе

MAC-блоков по

модулю  $m$

Схема блока ЕАС-ТМАС

по модулю  $2^{k-1}$

Схема КИХ-ЦФ

порядка  $K$  на основе

ЕАС-ТМАС-блоков

по модулю  $2^{k-1}$

**Положение 2. Архитектура цифрового фильтра в системе остаточных классов с модулями специального вида, реализующая ключевой вычислительный элемент обобщенной модели и обеспечивающая параллельную обработку сигналов**

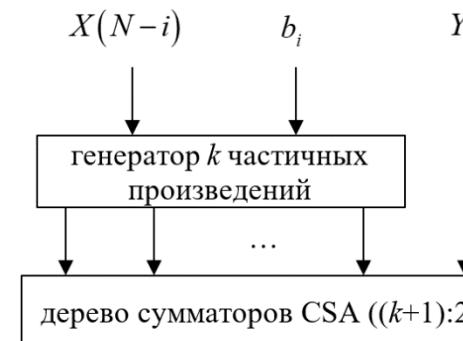

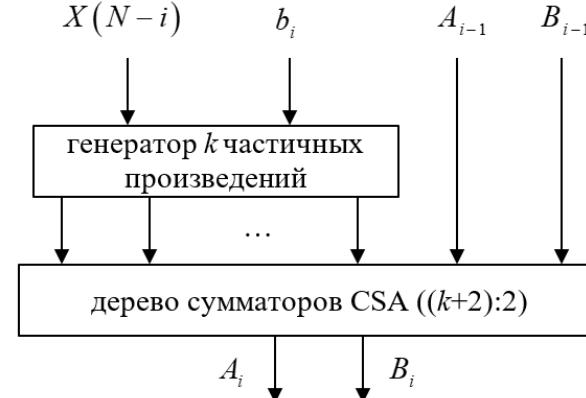

# Теоретическая оценка ресурсозатрат на цифровую фильтрацию в соответствии с разработанными моделью и архитектурой в системе остаточных классов

Разработанная модель представима в виде

$$\left\{ \begin{array}{l} \{m_1, m_2, \dots, m_n\} = \{2^{k_1}, 2^{k_2} - 1, 2^{k_3} - 1, \dots, 2^{k_n} - 1\}, \\ GCD(m_i, m_j) = 1, 2 \leq i < j \leq n, \\ \prod_{i=1}^n m_i \geq \max(X) \cdot \max(|b|) \cdot (K+1) \cdot 2, \\ |A_0 \cdot 2 + B_0|_{m_i} = |X(N) \cdot b_0|_{m_i}, \\ |A_j \cdot 2 + B_j|_{m_i} = |X(N-j) \cdot b_j + A_{j-1} + B_{j-1}|_{m_i}, 1 \leq j \leq K, \\ |Y(N)|_{m_i} = |A_K \cdot 2 + B_K|_{m_i}, \end{array} \right.$$

где:  $m_i$  ( $i = \overline{1, n}$ ) – модули СОК;  $GCD$  – наибольший общий делитель чисел;  $X(N)$  – отсчеты исходного сигнала;  $b_i$  – коэффициенты фильтра порядка  $K$ ;  $A_i$  и  $B_i$  – выходы дерева сумматоров с соответствующего блока;  $Y(N)$  – отсчеты обработанного сигнала.

Теоретический анализ ресурсозатрат на реализацию цифровой фильтрации сигналов в ПСС и СОК согласно разработанной модели показал превосходство модульных вычислений как по задержке, сократив ее от 1,3 до 2,6 раз, так и по аппаратным ресурсозатратам системы ЦОС, уменьшив их в 1,7-4,8 раза.

## Теоретическая оценка задержки

| Разрядность данных,<br>$k$ | ПСС | СОК      |          |           |

|----------------------------|-----|----------|----------|-----------|

|                            |     | 3 модуля | 4 модуля | 5 модулей |

| 8                          | 352 | 196      | 196      | 131       |

| 16                         | 463 | 306      | 277      | 242       |

| 32                         | 574 | 403      | 371      | 331       |

| 64                         | 685 | 514      | 473      | 430       |

## Теоретическая оценка площади

| Разрядность данных,<br>$k$ | ПСС    | СОК      |          |           |

|----------------------------|--------|----------|----------|-----------|

|                            |        | 3 модуля | 4 модуля | 5 модулей |

| 8                          | 8289   | 3553     | 4737     | 2650      |

| 16                         | 33009  | 14072    | 13059    | 10480     |

| 32                         | 131649 | 47004    | 42030    | 31865     |

| 64                         | 525633 | 187135   | 149210   | 109272    |

## **Основные результаты по положениям 1 и 2**

1. Выявлено, что наиболее экономными по совокупности ресурсозатрат на реализацию модулярных вычислений являются модули СОК специального вида:  $2^k$  и  $2^k - 1$ . Задержка сумматоров и умножителей при реализации вычислений по данным модулям аналогична задержке соответствующих блоков при реализации вычислений в ПСС с  $k$ -битным диапазоном. Аппаратные затраты на операции сложения и умножения по модулям вида  $2^k - 1$  незначительно превышают аппаратные затраты на выполнение этих операций в ПСС с  $k$ -битным диапазоном. Использование других модулей СОК повышает порядок сложности затрат на реализацию арифметических действий при ЦОС.

2. Установлено, что ЦОС с использованием ТМАС-блоков, передающих на следующее звено фильтра два числа вместо одного, позволяет использовать лишь один параллельно-префиксный сумматор в ЦФ за счет небольшого увеличения деревьев сумматоров с сохранением переноса и сократить время выполнения фильтрации одномерных сигналов на 22%-29% по сравнению с известной реализацией цифровой фильтрации на MAC-блоках.

3. Разработаны обобщенная модель усовершенствованной ЦОС в СОК и архитектура цифрового фильтра для параллельной обработки сигналов в СОК с модулями специального вида  $\{2^{k_1}, 2^{k_2} - 1, 2^{k_3} - 1, \dots, 2^{k_n} - 1\}$ , учитывающие все налагаемые на вычислительный диапазон ограничения и реализующие многоканальную обработку данных через КИХ-МЦФ по каждому модулю системы. Теоретический анализ ресурсозатрат на реализацию цифровой фильтрации сигналов в ПСС и СОК показал превосходство модулярных вычислений как по задержке, сократив ее от 1,3 до 2,6 раз, так и по аппаратным ресурсозатратам системы ЦОС, уменьшив их в 1,7-4,8 раза. Большее количество модулей СОК обеспечивает большее преимущество по эксплуатационным характеристикам системы ЦОС. Рост порядка ЦФ несколько увеличивает преимущества в скорости фильтрации и в экономии аппаратных ресурсов при использовании модулярных вычислений.

4. Теоретический анализ на основе UGM технических характеристик КИХ-МЦФ, построенного на основе СОК со сбалансированным набором модулей  $\{2^k - 1, 2^k, 2^k + 1\}$  и использующего специализированные вычислительные блоки, адаптированные под модули вида  $2^k + 1$ , продемонстрировал снижение аппаратных затрат от 2% до 10,3%, но вместе с тем показал повышение задержки вычислений от 8,3% до 53,3% в зависимости от порядка фильтра и разновидности блоков суммирования.

**Положение 1. Обобщенная модель усовершенствованной цифровой обработки сигналов в системе остаточных классов, обеспечивающая повышение производительности за счет системного объединения параллельной модулярной арифметики, блочной обработки данных, методов выполнения немодульных операций на основе дробных величин и масштабирования коэффициентов фильтров**

**Положение 2. Архитектура цифрового фильтра в системе остаточных классов с модулями специального вида, реализующая ключевой вычислительный элемент обобщенной модели и обеспечивающая параллельную обработку сигналов**

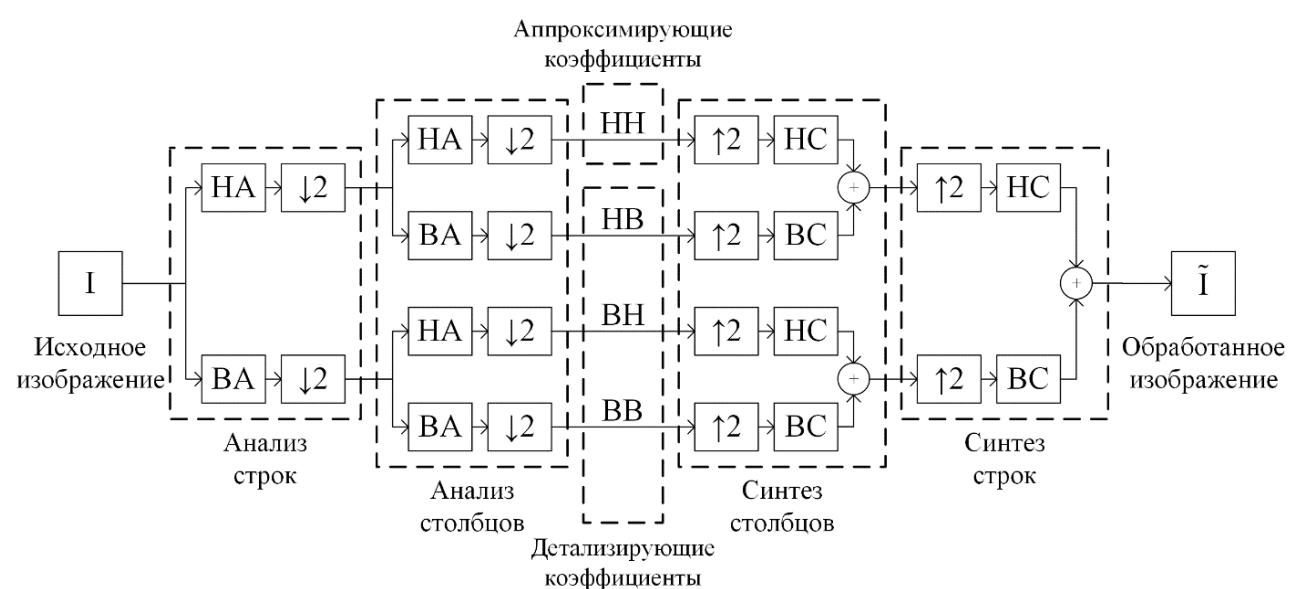

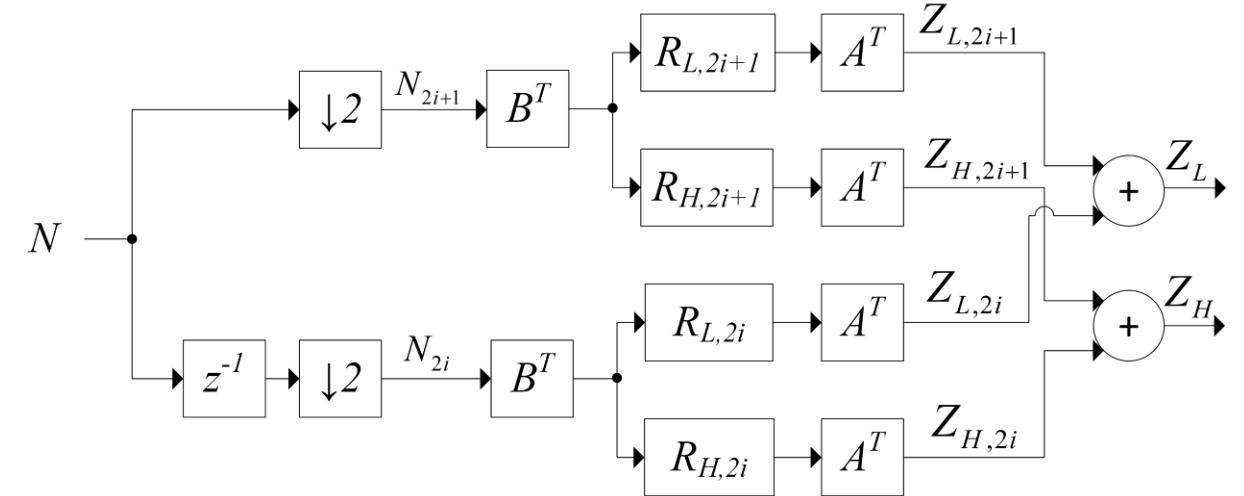

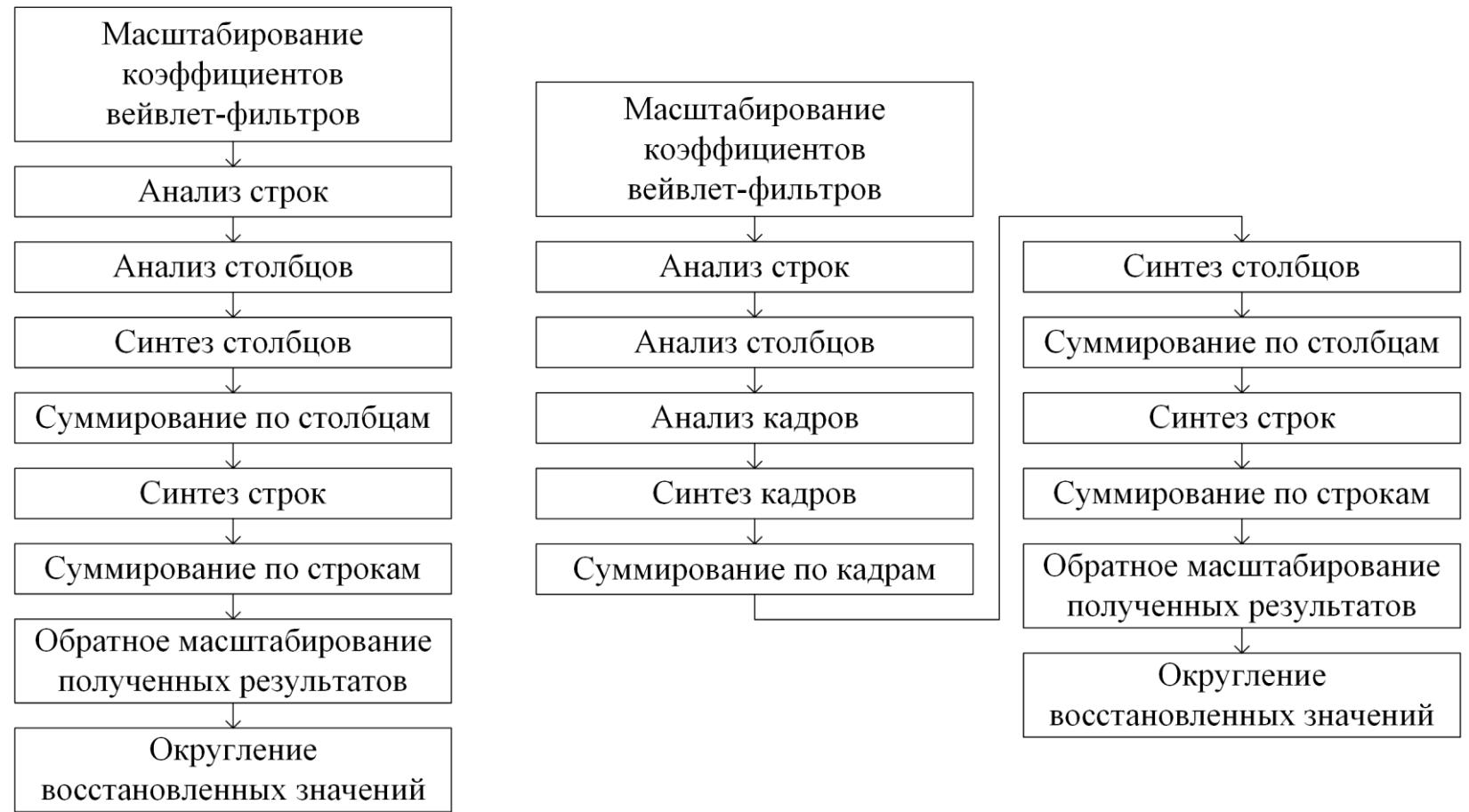

# Основные принципы одноуровневой вейвлет-обработки изображений

Свертка двумерных и трехмерных изображений с вейвлет-фильтрами  $F$  по их коэффициентам  $f_{F,i}$  ( $i = 1, \dots, l$ ) осуществляется по формулам

$$I'(x, y, z) = \sum_{i=1}^l I(x-i, y, z) \cdot f_{F,i},$$

$$I''(x, y, z) = \sum_{i=1}^l I'(x, y-i, z) \cdot f_{F,i},$$

$$I'''(x, y, z) = \sum_{i=1}^l I''(x, y, z-i) \cdot f_{F,i},$$

где:  $0 \leq x \leq X-1$ ,  $0 \leq y \leq Y-1$  и  $0 \leq z \leq Z-1$  – пространственные координаты цифрового изображения  $I(x, y, z)$ ,  $I'(x, y, z)$ ,  $I''(x, y, z)$  и  $I'''(x, y, z)$  – результаты свертки по строкам  $X$ , столбцам  $Y$  и кадрам  $Z$ , соответственно. При этом коэффициенты  $f_{F,i}$  различных видов вейвлет-фильтров  $F$  связаны соотношениями

$$f_{BA,i} = (-1)^i f_{HA,l-i+1}, f_{HC,i} = f_{HA,l-i+1},$$

$$f_{BC,i} = (-1)^{i+1} f_{HA,i}.$$

**Положение 3. Метод вейвлет-фильтрации сигналов с понижающей дискретизацией на основе блочной обработки данных, являющийся развитием обобщенной модели для ресурсоэффективной реализации многоуровневых преобразований**

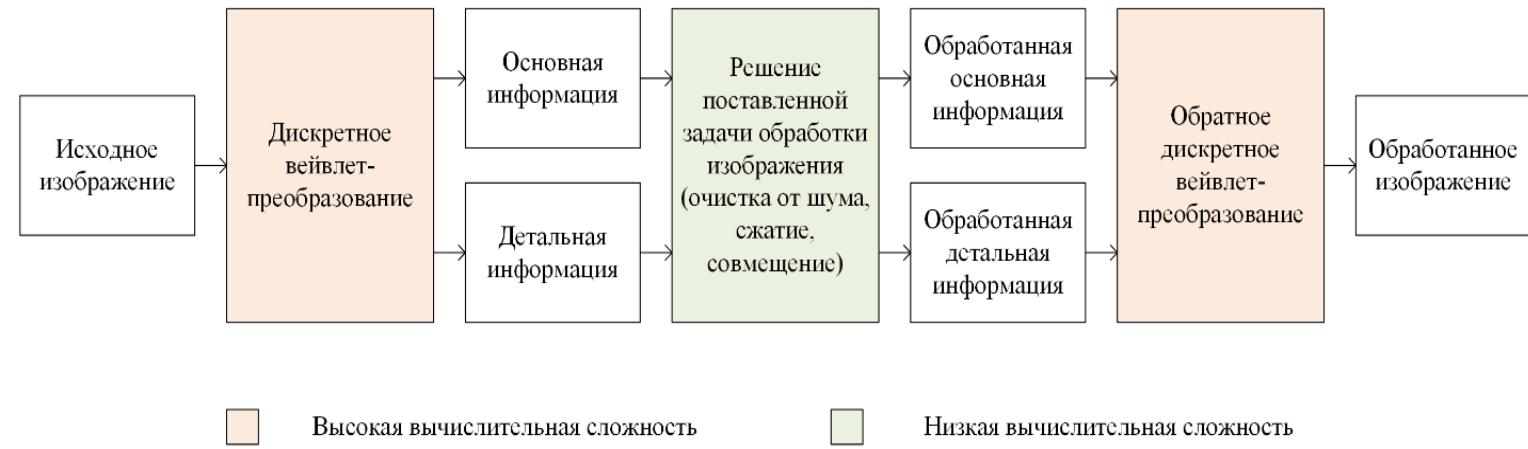

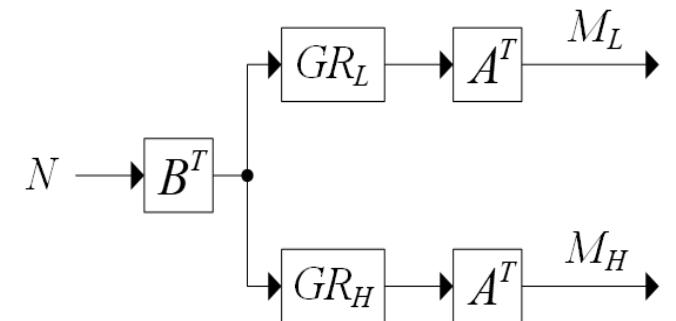

# Подход к высокоскоростной вейвлет-фильтрации сигналов на основе блочной обработки данных с уменьшением количества используемых умножений

Вейвлет-фильтрация двумерных сигналов, осуществляется по формуле (1), реализована в виде матричных вычислений, представленных в формуле (2).

$$I(x, y) = \sum_{i=1}^r I(x-i, y) \cdot r_i, \quad I'(x, y) = \sum_{i=1}^r I(x, y-i) \cdot r_i, \quad (1)$$

где  $I(x, y)$  – пиксели исходного двумерного изображения;

$R = (r_1, r_2, r_3, \dots, r_{r-1}, r_r)$  – одномерный вейвлет-фильтр порядка  $r$ .

$$M = A^T ((GR) \odot (B^T N)), \quad (2)$$

где:  $M$  – фрагмент обработанного изображения размером  $m \times 1$ ;  $R$  – ВФ размера  $r \times 1$ ;  $N$  – исходный фрагмент изображения размером  $n \times 1$  ( $n = m + r - 1$ );  $A^T$ ,  $G$ ,  $B^T$  – матрицы преобразования размеров  $m \times n$ ,  $n \times r$ ,  $n \times n$ , соответственно;  $\odot$  – оператор поэлементного матричного умножения. В случае одномерной фильтрации методом Винограда обозначается как  $F(m, r)$  и содержит размер  $m$  фрагментов обработанного изображения и порядок  $r$  используемого вейвлета. Вейвлет-обработка реализована параллельно по 2 вычислительных каналам с применением составленных вспомогательных матриц преобразования. Количество используемых операций умножений значительно снижено благодаря возможности априорной организации через масштабирование и сложение, обладающие значительно меньшей вычислительной сложностью.

Вейвлет-фильтрация прямым методом

Вейвлет-фильтрация на основе матричных вычислений методом Винограда

# Составление вспомогательных матриц преобразования для организации цифровой вейвлет-фильтрации с использованием блочной обработки данных

**Алгоритм 1** Составление вспомогательной матрицы преобразования  $A^T$

**Входные данные:** матрица Вандермонда  $V$

**Выходные данные:** матрица преобразования  $A^T$

- 1: **рассчитать**  $V^T$

- 2:  $A^T(i,j) = V^T(i,j)$ , где  $i = \overline{1,m}$  и  $j = \overline{1,n}$

- 3:  $A^T(m,n) = 1$

**Алгоритм 2** Составление вспомогательной матрицы преобразования  $G$

**Входные данные:** матрица Вандермонда  $V$

**Выходные данные:** матрица преобразования  $G$

- 1: **рассчитать**  $V^{-T}$

- 2: **для**  $i$  от 1 до  $n$

- 3:     **для**  $j$  от 1 до  $n$

- 4:          $y_j = den(V^{-T}(i,j))$

- 5:     **конец**

- 6:      $z_i = LCM\{y_j\}$

- 7:     **конец**

- 8:      $G(i,j) = \frac{V(i,j)}{z_i}$ , где  $i = \overline{1,n}$  и  $j = \overline{1,r}$

- 9:      $G(n,r) = 1$

**Алгоритм 3.1.3** Составление вспомогательной матрицы преобразования  $B^T$

**Входные данные:** матрица Вандермонда  $V$

**Выходные данные:** матрица преобразования  $B^T$

- 1: **рассчитать**  $V^{-T}$

- 2: **для**  $i$  от 1 до  $n$

- 3:     **для**  $j$  от 1 до  $n$

- 4:          $y_j = den(V^{-T}(i,j))$

- 5:     **конец**

- 6:      $z_i = LCM\{y_j\}$

- 7:     **конец**

- 8:      $B^T(i,j) = V^{-T}(i,j)z_i$ , где  $i = \overline{1,n}$  и  $j = \overline{1,n}$

# Расчет необходимого количества операций сложения и умножения для вейвлет-фильтрации двумерных сигналов различными методами

Количество сложений и умножений при цифровой фильтрации двумерных сигналов (изображений) рассчитывается по следующим правилам:

1. Количество умножений при использовании прямого метода равно  $2r$ , где  $r$  – порядок вейвлета.

2. Количество сложений при использовании прямого метода равно  $2(r - 1)$ .

3. Количество умножений при использовании матричных вычислений методом Винограда равно  $2n$ , где  $n$  – размер обрабатываемого фрагмента исходного изображения.

4. Количество сложений при использовании матричных вычислений методом Винограда равно уменьшенной на 1 сумме единиц в двоичной записи элементов каждой строки матриц  $A^r$  и  $B^r$ .

5. Удельный вес пикселя при использовании матричных вычислений методом Винограда вычисляется делением количества операций (умножений и сложений), необходимых для получения фрагмента обработанного изображения, на число  $m$  пикселей данного фрагмента.

| Порядок вейвлета | Метод    | Количество слагаемых в каждой строке матрицы |                                               |

|------------------|----------|----------------------------------------------|-----------------------------------------------|

|                  |          | $A^r$                                        | $B^r$                                         |

| 4                | $F(2,4)$ | <b>4,4</b>                                   | <b>4,3,4,2,4</b>                              |

|                  | $F(3,4)$ | <b>5,4,5</b>                                 | <b>4,4,4,4,4,4</b>                            |

|                  | $F(4,4)$ | <b>6,5,5,6</b>                               | <b>8,7,6,6,9,4,8</b>                          |

|                  | $F(5,4)$ | <b>7,6,6,6,7</b>                             | <b>8,8,8,8,8,8,8,8</b>                        |

| 6                | $F(2,6)$ | <b>6,6</b>                                   | <b>8,7,6,6,9,4,8</b>                          |

|                  | $F(3,6)$ | <b>7,6,7</b>                                 | <b>8,8,8,8,8,8,8,8</b>                        |

|                  | $F(4,6)$ | <b>8,7,7,8</b>                               | <b>16,17,14,14,12,12,18,8,16</b>              |

|                  | $F(5,6)$ | <b>9,8,8,8,9</b>                             | <b>15,16,16,16,16,16,16,16,15</b>             |

|                  | $F(6,6)$ | <b>10,9,9,9,9,10</b>                         | <b>30,31,20,34,29,28,30,24,33,15,30</b>       |

|                  | $F(7,6)$ | <b>11,10,10,10,10,10,11</b>                  | <b>26,30,30,32,32,30,30,32,32,30,30,26</b>    |

| 8                | $F(2,8)$ | <b>8,8</b>                                   | <b>16,17,14,14,12,12,18,8,16</b>              |

|                  | $F(3,8)$ | <b>9,8,9</b>                                 | <b>15,16,16,16,16,16,16,16,15</b>             |

|                  | $F(4,8)$ | <b>10,9,9,10</b>                             | <b>30,31,20,34,29,28,30,24,33,15,30</b>       |

|                  | $F(5,8)$ | <b>11,10,10,10,11</b>                        | <b>26,30,30,32,32,30,30,32,32,30,30,26</b>    |

|                  | $F(6,8)$ | <b>12,11,11,11,11,12</b>                     | <b>52,53,48,58,36,56,54,56,55,45,54,26,52</b> |

Положение 3. Метод вейвлет-фильтрации сигналов с понижающей дискретизацией на основе блочной обработки данных, являющийся развитием обобщенной модели для ресурсоэффективной реализации многоуровневых преобразований

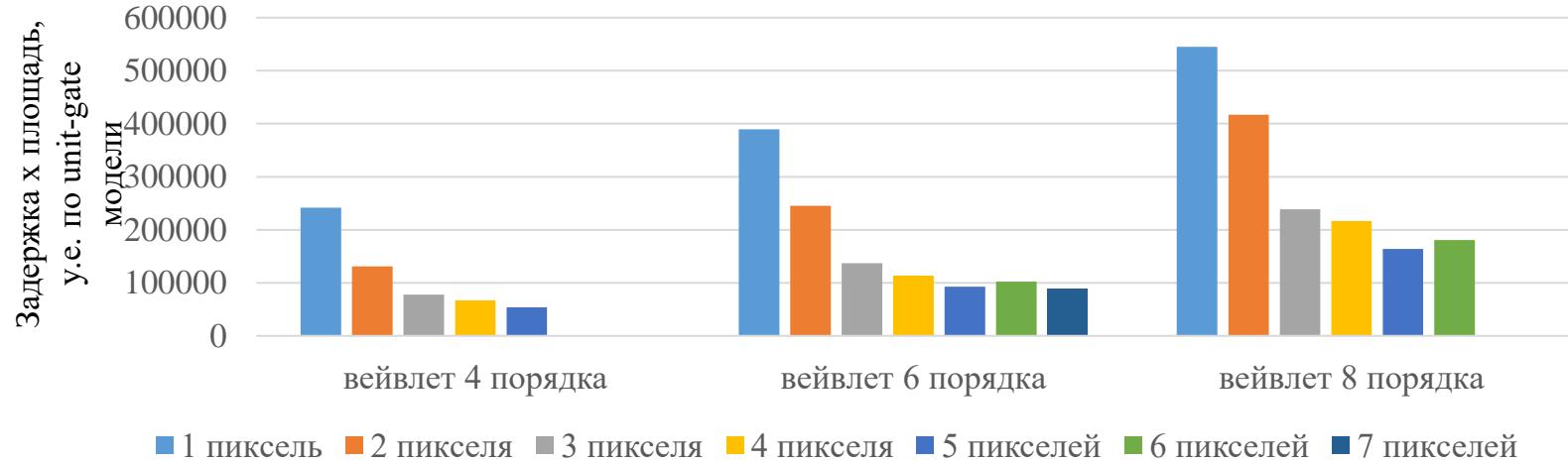

# Теоретическая оценка ресурсозатрат на реализацию вейвлет-фильтрации двумерных сигналов с использованием различных подходов (начало)

Для оценки временных и аппаратных ресурсозатрат на реализацию методов вейвлет-фильтрации двумерных сигналов (изображений) использована методика unit-gate model (UGM). В соответствии с данной методикой обозначим характеристики используемых умножителей и многовходовых сумматоров.

1. Задержка умножителя двух чисел разрядности  $k$  вычисляется по формуле  $U_{delay}(mul(k)) = 8,8\log_2 k + 5$ .

2. Площадь умножителя двух чисел разрядности  $k$  вычисляется по формуле  $U_{area}(mul(k)) = 3k \log_2 k + 8k^2 - 11k + 1$ .

3. Задержка сумматора  $p$  чисел разрядности  $k$  вычисляется по формуле  $U_{delay}(add(k, p)) = 6,8\log_2 p + 2\log_2 k + 4$ .

4. Площадь сумматора  $p$  чисел разрядности  $k$  вычисляется по формуле  $U_{area}(add(k, p)) = 3k \log_2 k + 7kp - 11k + 1$ .

| Порядок вейвлета | Метод    | Размер фрагмента | Для каждого фрагмента |          | Удельный вес пикселя |          |

|------------------|----------|------------------|-----------------------|----------|----------------------|----------|

|                  |          |                  | Умножения             | Сложение | Умножения            | Сложение |

| 4                | Прямой   | 1                | 8                     | 6        | 8,00                 | 6,00     |

|                  | $F(2,4)$ | 2                | 10                    | 24       | 5,00                 | 12,00    |

|                  | $F(3,4)$ | 3                | 12                    | 40       | 4,00                 | 13,33    |

|                  | $F(4,4)$ | 4                | 14                    | 77       | 3,50                 | 19,25    |

|                  | $F(5,4)$ | 5                | 16                    | 110      | 3,20                 | 22,00    |

| 6                | Прямой   | 1                | 12                    | 10       | 12,00                | 10,00    |

|                  | $F(2,6)$ | 2                | 14                    | 61       | 7,00                 | 30,50    |

|                  | $F(3,6)$ | 3                | 16                    | 90       | 5,33                 | 30,00    |

|                  | $F(4,6)$ | 4                | 18                    | 169      | 4,50                 | 42,25    |

|                  | $F(5,6)$ | 5                | 20                    | 222      | 4,00                 | 44,40    |

|                  | $F(6,6)$ | 6                | 22                    | 382      | 3,67                 | 63,67    |

|                  | $F(7,6)$ | 7                | 24                    | 478      | 3,43                 | 68,29    |

| 8                | Прямой   | 1                | 16                    | 14       | 16,00                | 14,00    |

|                  | $F(2,8)$ | 2                | 18                    | 140      | 9,00                 | 70,00    |

|                  | $F(3,8)$ | 3                | 20                    | 194      | 6,67                 | 64,67    |

|                  | $F(4,8)$ | 4                | 22                    | 350      | 5,50                 | 87,50    |

|                  | $F(5,8)$ | 5                | 24                    | 442      | 4,80                 | 88,40    |

Положение 3. Метод вейвлет-фильтрации сигналов с понижающей дискретизацией на основе блочной обработки данных, являющийся развитием обобщенной модели для ресурсоэффективной реализации многоуровневых преобразований

# Теоретическая оценка ресурсозатрат на реализацию вейвлет-фильтрации двумерных сигналов с использованием различных подходов (начало)

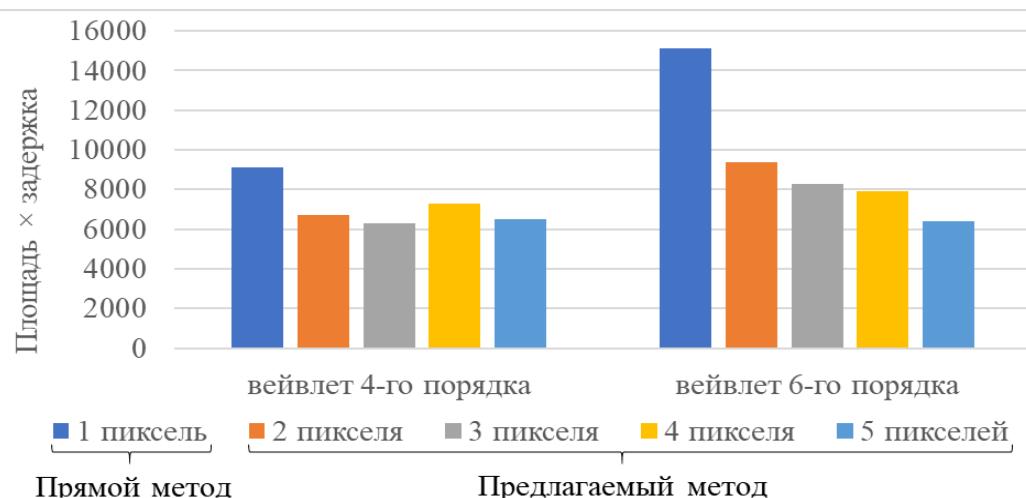

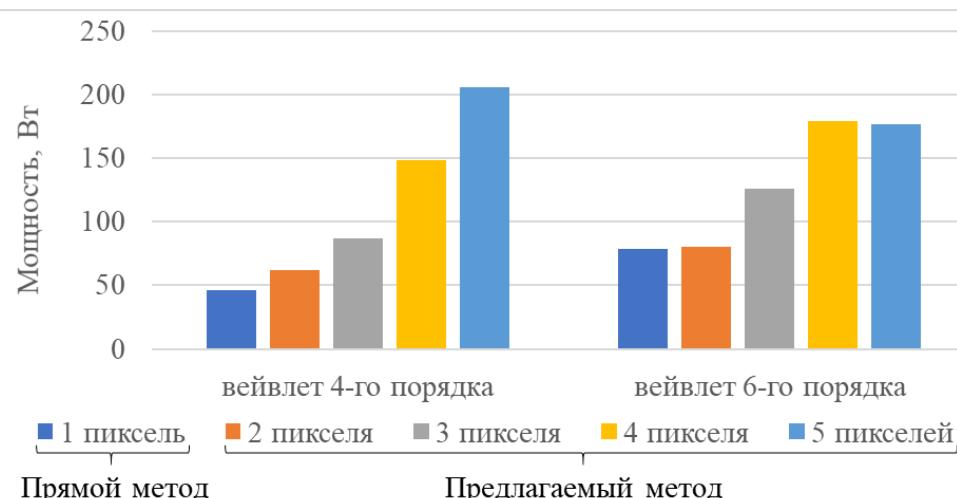

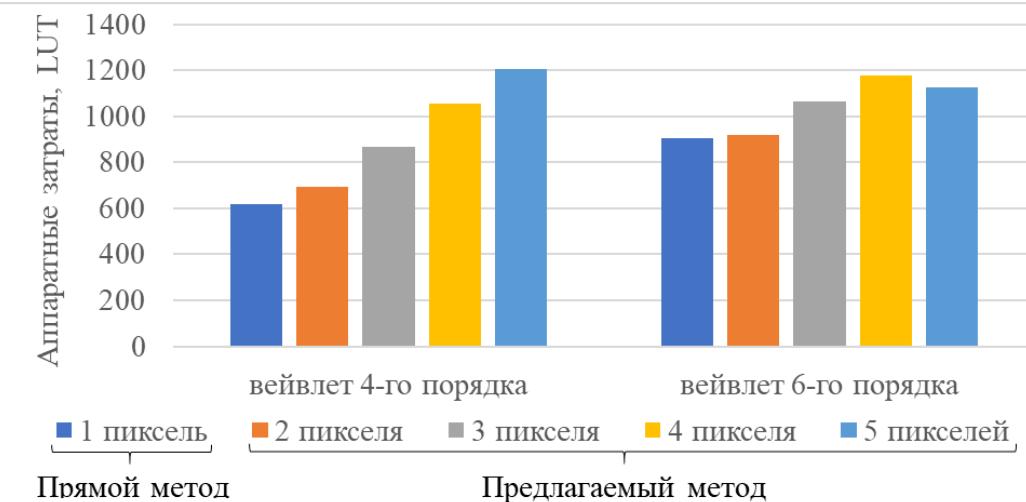

Результаты оценки ресурсозатрат на реализацию вейвлет-фильтрации с использованием различных подходов показали, что организация матричных вычислений повышает скорость обработки сигналов до 73,62% и уменьшает аппаратные затраты до 34,03% за счет понижения количества используемых операций умножения.

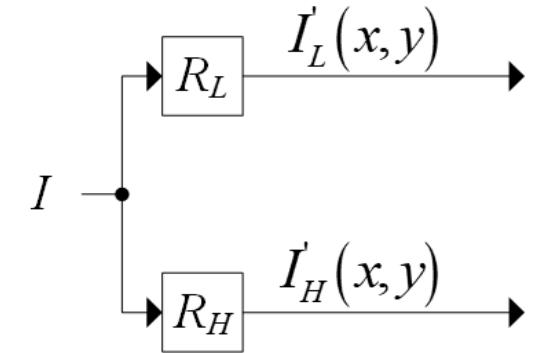

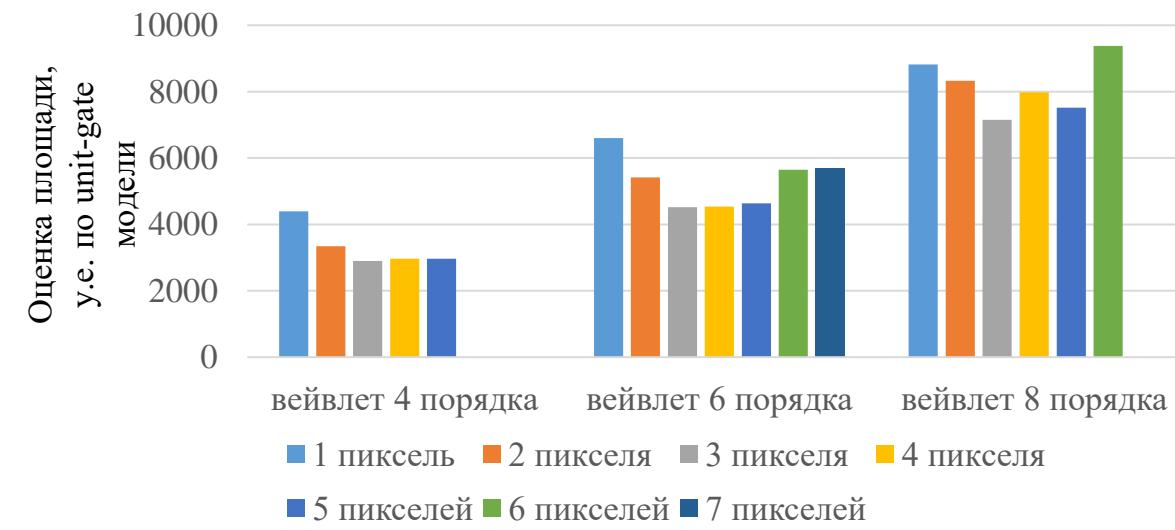

# Метод организации блочной обработки данных при вейвлет-обработке цифровых сигналов с понижающей дискретизацией

В общем случае одномерная цифровая фильтрация на основе блочной обработки данных методом Винограда  $F(m, r, d)$  с фрагментами изображения размера  $F(m, r, d)$ , порядком используемого фильтра  $F(m, r, d)$  и уменьшением частоты дискретизации в  $d$  раз реализуется по формуле

$$F(m, r, d) = s_2 \cdot F(m, s_1 + 1) + (d - s_2) \cdot F(m, s_1),$$

где  $s_1$  и  $s_2$  – неполное частное и остаток от деления  $r$  на  $d$ , соответственно. В частном случае, когда  $d$  делит  $r$ , формула примет вид

$$F(m, r, d) = d \cdot F(m, s_1).$$

Вычисления организуются согласно представленной схеме, в которой  $Z_L$  и  $Z_H$  – фрагменты изображения, обработанные методом Винограда  $F(m, r, 2)$  с использованием вейвлет-фильтров  $R_L$  и  $R_H$ , соответственно. Выбранный фрагмент обрабатываемого изображений подразделяется на две составляющие, одна из которых включает в себя четные отсчеты исходного сигнала, а другая – нечетные. Таким образом осуществляется распараллеливание вычислений по нескольким каналам. Поэлементное умножение выполняется однократно для двух матриц-столбцов порядка. Все остальные вычисления реализуются с использованием сложений с априори рассчитанными константными величинами.

## **Основные результаты по положению 3**

1. На основе анализа подходов к организации блочной обработки данных МВ для повышения скорости работы методов цифровой фильтрации одномерных и многомерных сигналов при их реализации на современных средствах вычислительной техники предложен способ выбора наиболее эффективных с точки вычислительной сложности наборов точек, используемых для оценки эксплуатационных характеристик систем ЦОС.

2. Предложена методика для оценки эксплуатационных характеристик системы ЦОС, реализующей цифровую фильтрацию на основе блочной обработки данных с использованием МВ. Рассмотрены различные параметры МВ и рассчитано количество используемых операций сложения и умножения на основе численных значений коэффициентов вспомогательных матриц преобразования, составление которых выполняется априори и не требует затрат в процессе эксплуатации устройства, реализующего методы обработки сигналов на основе МВ. Результаты оценки на основе предложенной методики с использованием UGM показали, что организация блочной обработки данных МВ снижает вычислительную сложность цифровой фильтрации изображений до 84% при неизменном качестве обработки данных.

3. Разработан подход к реализации вейвлет-фильтрации двумерных сигналов на основе блочной обработки данных. Вейвлет-обработка реализована параллельно по 2 вычислительных каналам с применением составленных вспомогательных матриц преобразования. Количество используемых операций умножений значительно снижено благодаря возможности априорной организации через масштабирование и сложение, обладающие значительно меньшей вычислительной сложностью. Предложенный подход сократил вычислительную сложность цифровой фильтрации двумерного сигнала до 72,9%. Оценка эксплуатационных характеристик системы на основе предложенной методики показала, что разработанный подход повышает скорость вычислений до 73,62% и уменьшает аппаратные затраты до 34,03% за счет понижения количества используемых операций умножения.

4. Разработан метод организации блочной обработки данных при одномерной цифровой фильтрации двумерных сигналов с понижающей дискретизацией. Выведены формулы для реализации сверточных вычислений при любых значениях шага свертки одномерного фильтра с двумерным сигналом в виде комбинации МВ с различными параметрами.

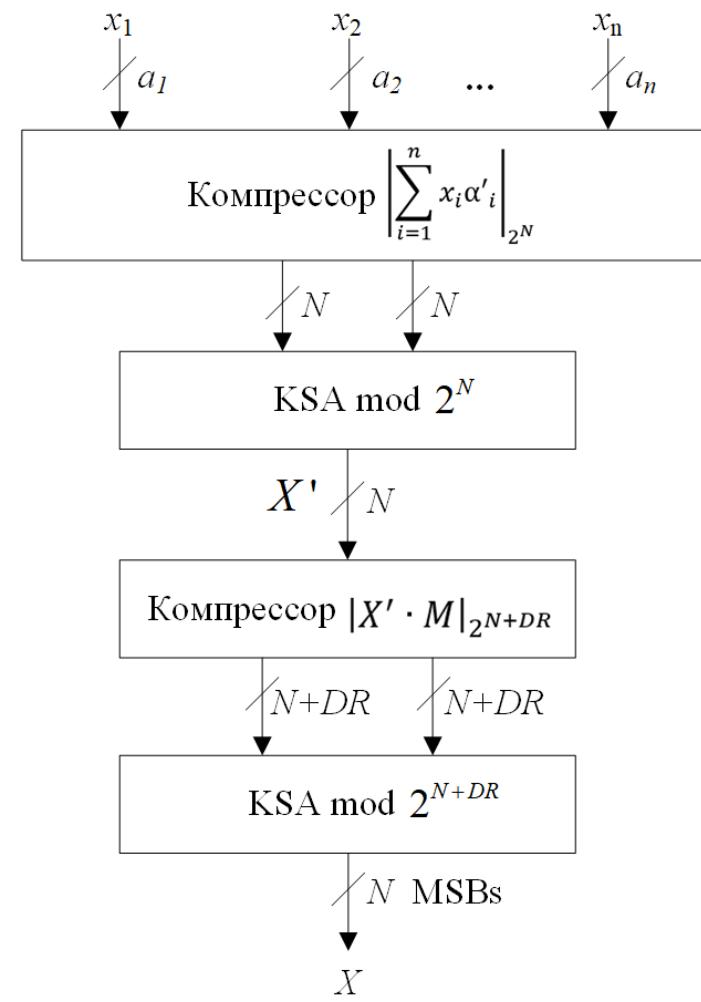

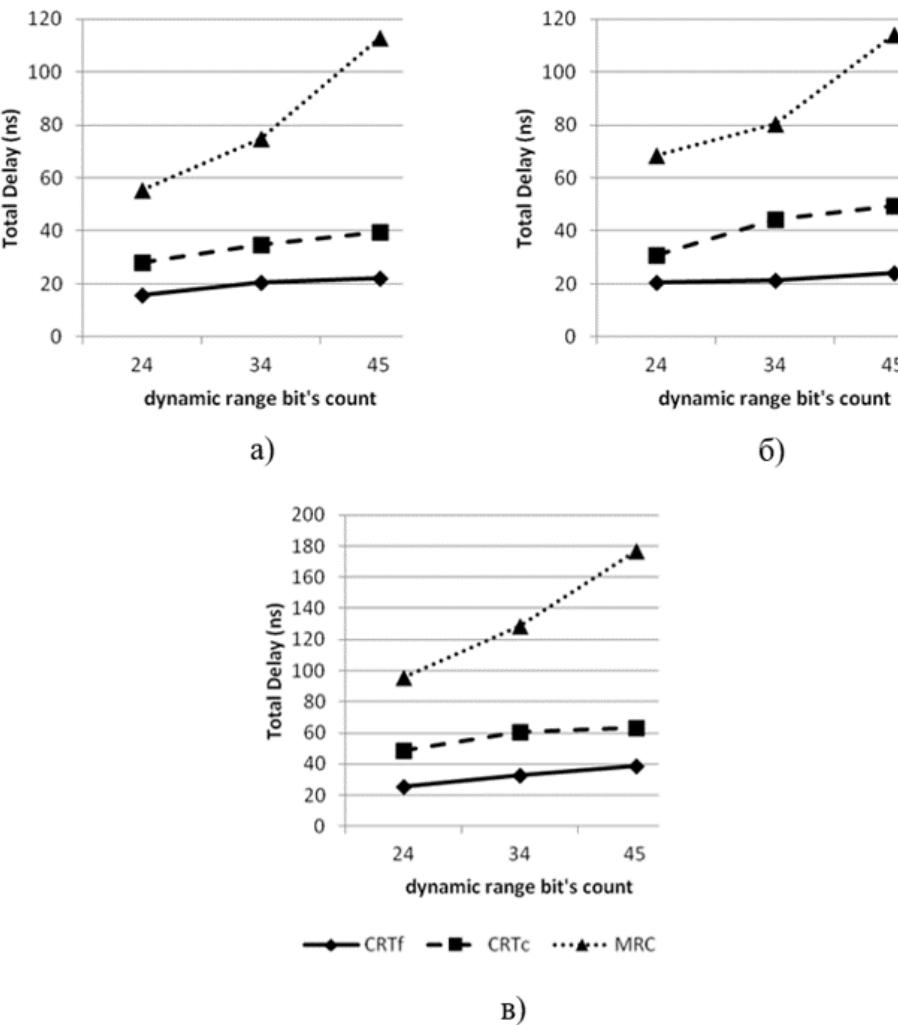

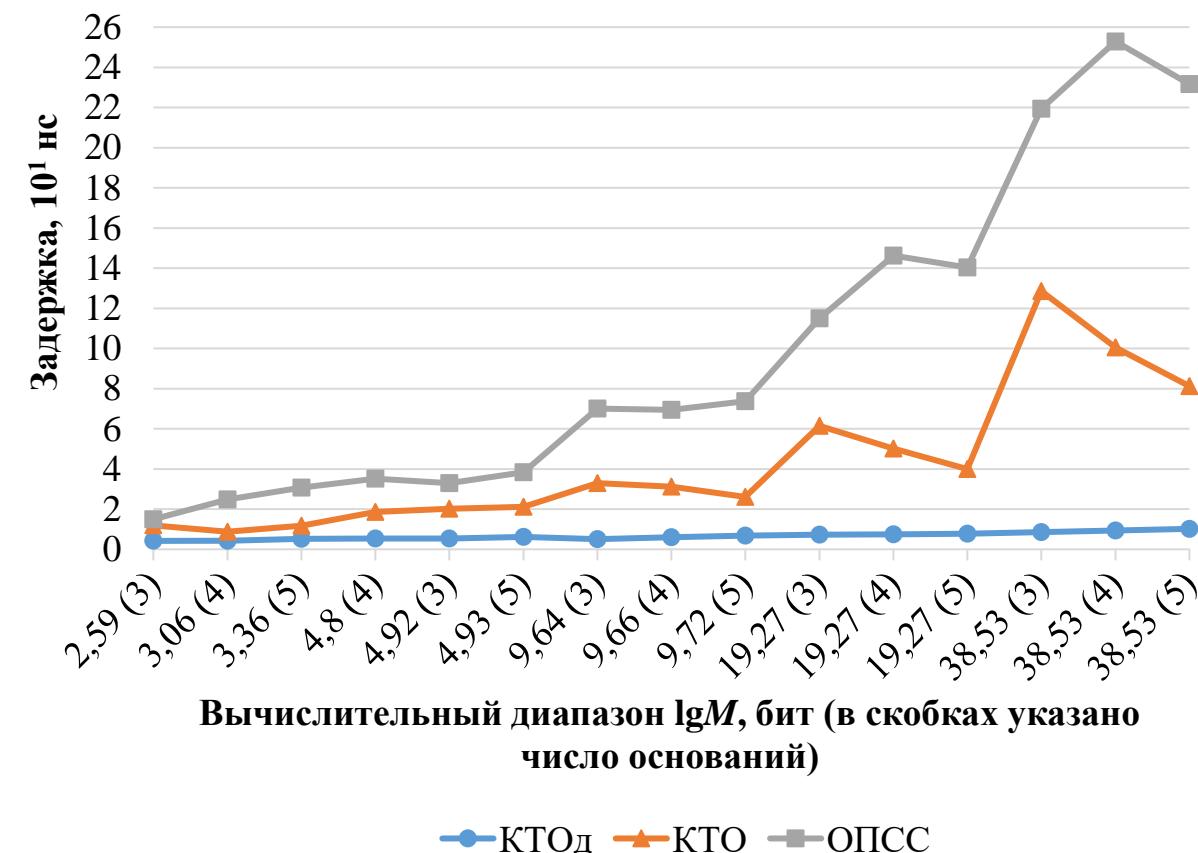

# Метод обратного преобразования чисел из СОК в ПСС на основе дробных величин и архитектура для его реализации (начало)

Разработана модифицированная версия Китайской теоремы об остатках (КТО) с дробными величинами (КТОд) для выполнения преобразования остатков в двоичный код. В системе остаточных классов (СОК) с модулями  $\{m_1, m_2, \dots, m_n\}$  число  $X$  представляется в виде  $\{x_1, x_2, \dots, x_n\}$ , где  $x_i \equiv |X|_{m_i}$ . При этом обратное преобразование выполняется по формуле

$$X = \left| \sum_{i=1}^n \left( |M_i^{-1}|_{m_i} M_i \right) x_i \right|_M , \quad (1)$$

где  $M_i = M/m_i$ , а выражение  $|M_i^{-1}|_{m_i}$  означает обратный элемент для  $M_i$  в мультиплексивной группе кольца вычетов по модулю  $m_i$ . Реализация операции по формуле (1) на современных средствах вычислительной техники является ресурсозатратной, в связи с чем основной целью большинства исследований обратного преобразования является максимальное упрощение данной операции. Одним из самых эффективных подходов является модификация традиционной КТО, заключающаяся в аппроксимации относительного положения чисел на числовой прямой. Этот подход получил название КТОд. В основе КТОд лежит идея упрощения вычислений за счет изменения выражения (1) для выявления положения этого числа.

# Метод обратного преобразования чисел из СОК в ПСС на основе дробных величин и архитектура для его реализации (окончание)

Для этого поделим обозначенное выражение на диапазон  $M$ :

$$\frac{X}{M} = \left| \sum_{i=1}^n x_i \frac{\left| M_i^{-1} \right|_{m_i} M_i}{M} \right|_1 = \left| \sum_{i=1}^n \alpha_i x_i \right|_1 \quad (2),$$

где  $\left| \cdot \right|_1$  представляет собой операцию нахождения дробной части числа, и  $\alpha_i = \frac{\left| M_i^{-1} \right|_{m_i} M_i}{M}$ .

В этом случае формула (2) преобразуется к виду  $\frac{X}{M} = \left| \sum_{i=1}^n x_i \alpha_i \right|_1$ . Данное выражение можно

записать в виде  $X = \frac{XM}{2^K}$ , где  $X' = \left\lfloor 2^K \frac{X}{M} \right\rfloor = \left| \sum_{i=1}^n x_i \alpha'_i \right|_{2^N}$ .

Данный подход позволяет избежать операции вычисления остатка от деления на модуль  $M$ , тем самым уменьшив ресурсозатраты при аппаратной реализации модульных вычислений. Предложенный метод вычисления существенно проясняет требуемое количество двоичных значений аналогичным избыточные оценкам, что позволяет вычислить с минимальным требуемым количеством обрабатываемых бит.

## Метод определения знака числа, представленного в СОК, на основе дробных величин

1. Для СОК с модулями  $\{m_1, m_2, \dots, m_n\}$  предварительно вычисляются константы  $M = m_1 m_2 \dots m_n$ ,  $\mu = -n + \sum_{i=1}^n m_i$ ,  $N = \lceil \log_2(M\mu) \rceil$  и  $\alpha_i = \left( \left| M_i^{-1} \right|_{m_i} M_i \right) / M$ .

2. Для констант  $k_i$ , определенных в пункте 1, определяются дробные величины  $[F(\alpha_i)]_{2^{-N}}$  и  $[F(\alpha_i)]_{2^{-\tilde{N}}}$ , где  $F(\alpha_i)$  – бесконечная дробь в двоичной системе счисления, равная  $\alpha_i$ , и  $\tilde{N} < N$ .

3. С целью выявления знака исходного числа рассчитывается значение величины  $[F(X/M)]_{2^{-\tilde{N}}} = \left| \sum_{i=1}^n x_i [F(\alpha_i)]_{2^{-\tilde{N}}} \right|_1$ .

4. Из условия  $0 < \left[ F\left(\frac{X}{M}\right) \right]_{2^{-\tilde{N}}} < \frac{1}{2} - 2^{-\tilde{N}}\mu$  следует, что исходное число больше нуля. Из условия  $\frac{1}{2} < \left[ F\left(\frac{X}{M}\right) \right]_{2^{-\tilde{N}}} < 1 - 2^{-\tilde{N}}\mu$  следует, что оно меньше нуля.

5. Если ни одно из условий пункта 4 не выполнено, то число  $X$  попало в одну из зон неопределенности, поэтому требуется уточняющая итерация. Вычисляется  $[F(X/M)]_{2^{-N}} = \left| \sum_{i=1}^n x_i [F(\alpha_i)]_{2^{-N}} \right|_1$ .

6. Если  $0 < [F(X/M)]_{2^{-N}} < 0,5$ , то число  $X$  положительное. Если  $0,5 < [F(X/M)]_{2^{-N}} < 1$ , то число  $X$  отрицательное.

## **Метод сравнения чисел в СОК на основе дробных величин и архитектура для его реализации (начало)**

Для решения задачи сравнения двух чисел  $X$  и  $Y$  в модулярном коде представлен оригинальный подход на основе дробных величин, в соответствии с которым необходимо выполнить следующую последовательность действий.

1. Установить, какие знаки имеют исходные числа.

2. В случае, когда оба числа являются беззнаковыми, если их разность больше нуля, то уменьшаемое число превосходит вычитаемое.

3. В случае, когда оба числа имеют одинаковый знак, выполняется вычисление  $|X/M - Y/M|_1$ .

4. В случае, когда числа имеют противоположные знаки, первое число больше, если выполняется условие  $0 \leq |X/M - Y/M|_1 < 0,5$ , и второе число больше, если выполняется условие  $0,5 \leq |X/M - Y/M|_1 < 1$ .

Выигрыш по ресурсозатратам на реализацию данной операции на современных средствах вычислительной техники должен обеспечиваться значительно уменьшенным количеством выполняемых операций при реализации арифметической обработки данных в модулярном коде.

# Метод и архитектура сравнения чисел в СОК на дробных величин и архитектура для его реализации (окончание)

На слайде представлена схема реализации метода сравнения чисел в СОК с использованием Китайской теоремы об остатках с дробными величинами (КТОд). На вход устройства поступают два числа  $X = (x_1, x_2, \dots, x_n)$  и  $Y = (y_1, y_2, \dots, y_n)$ , представленные в СОК с основаниями  $\{m_1, m_2, \dots, m_n\}$ , которым соответствуют разрядности  $\{a_1, a_2, \dots, a_n\}$ . Умножение на константы реализовано с помощью компрессора и сумматора KSA по модулю  $2^k$ . Далее значение позиционных характеристик передается на компаратор, который реализует операцию сравнения.

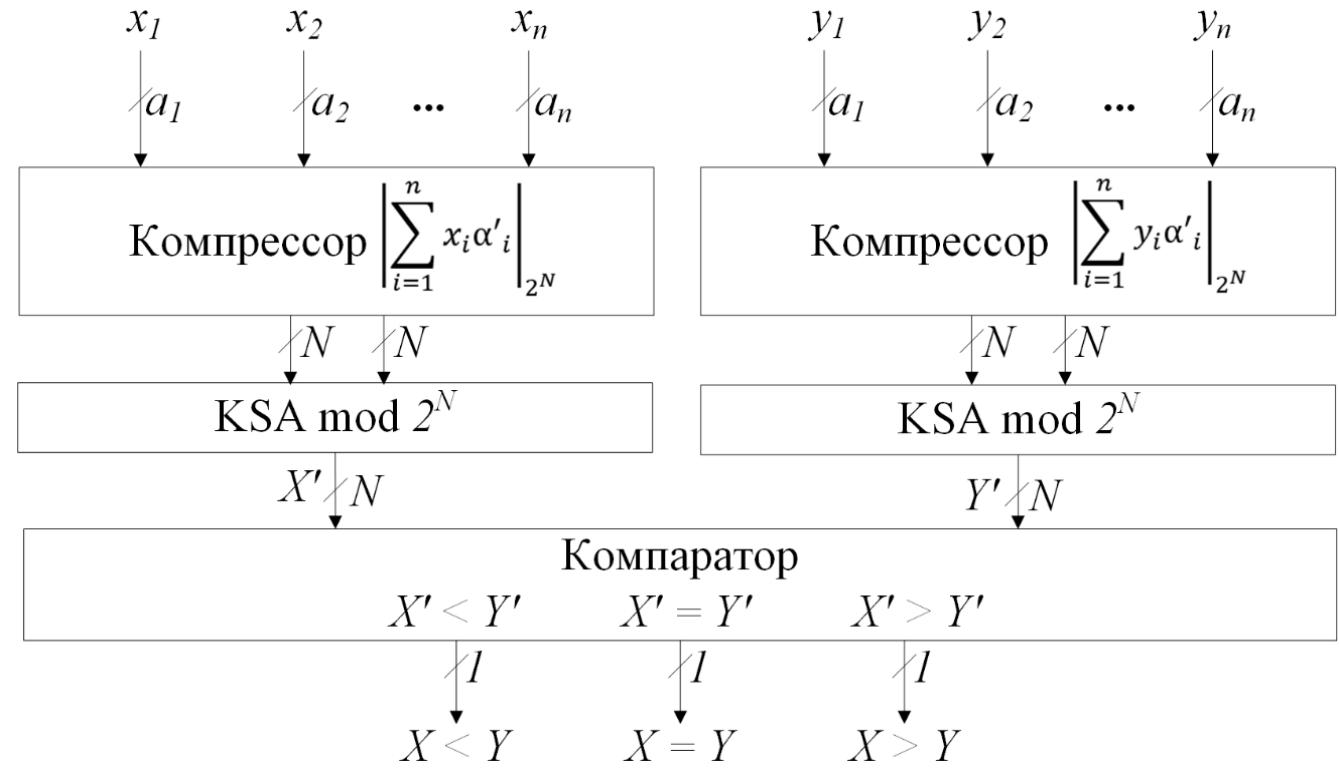

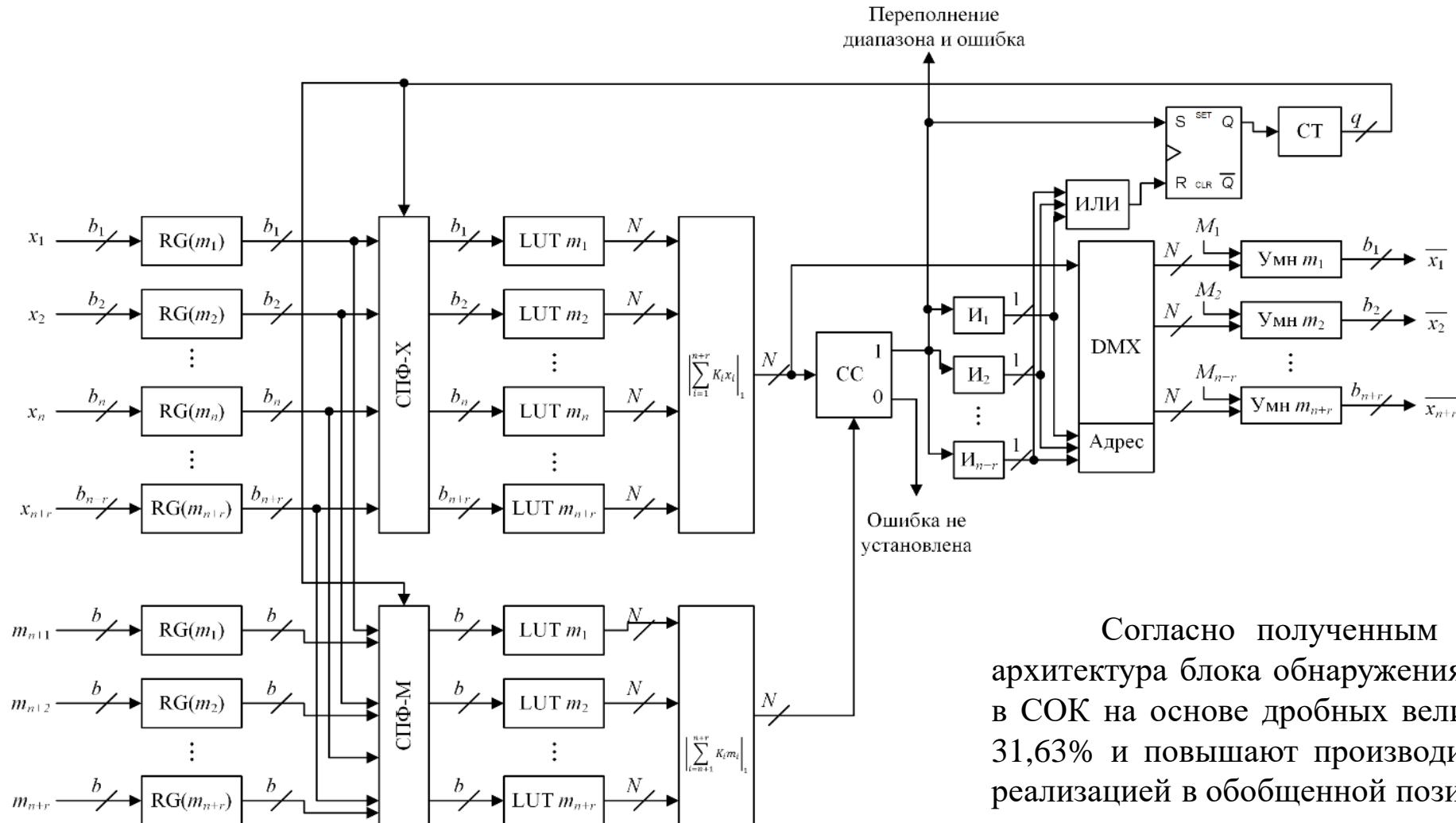

# Метод и архитектура блока обнаружения, локализации и исправления ошибок в СОК на основе дробных величин (начало)

Пусть СОК содержит  $n$  рабочих каналов и  $r$  контрольных каналов  $n+1, \dots, n+r$ , функционирующих одновременно и параллельно. Тогда обнаружения, локализации и исправления ошибок в СОК на основе КТОд описывается следующей последовательностью действий:

1. Вычисление констант СОК  $\alpha_i = \frac{\left| M_i^{-1} \right|_{m_i}}{m_i}$  с требуемой точностью, где  $i = 1, 2, \dots, n+r$ .

2. Вычисление приближенных значений  $\alpha_i x_i$  и запись их в LUT-таблицы, где  $\alpha_i$  – константы, найденные в пункте 1,  $1 \leq \alpha_i \leq m_i - 1$ . Адресами выборки значений  $\alpha_i x_i$  являются  $x_i$ , где  $i = 1, \dots, n+r$ .

3. Вычисление позиционной характеристики величины  $\bar{X}$ .

4. Конструирование некоторых правил  $\Psi_j$ , где  $j = 1, 2, 3$ , согласно которым выполняется  $j$ -я немодульная операция (обнаружение ошибки, переполнение и локализация ошибочного разряда), а также исправление ошибочного числа на основе восстановления позиционного числа  $X$  по остаткам.

# Метод и архитектура блока обнаружения, локализации и исправления ошибок в СОК на основе дробных величин (окончание)

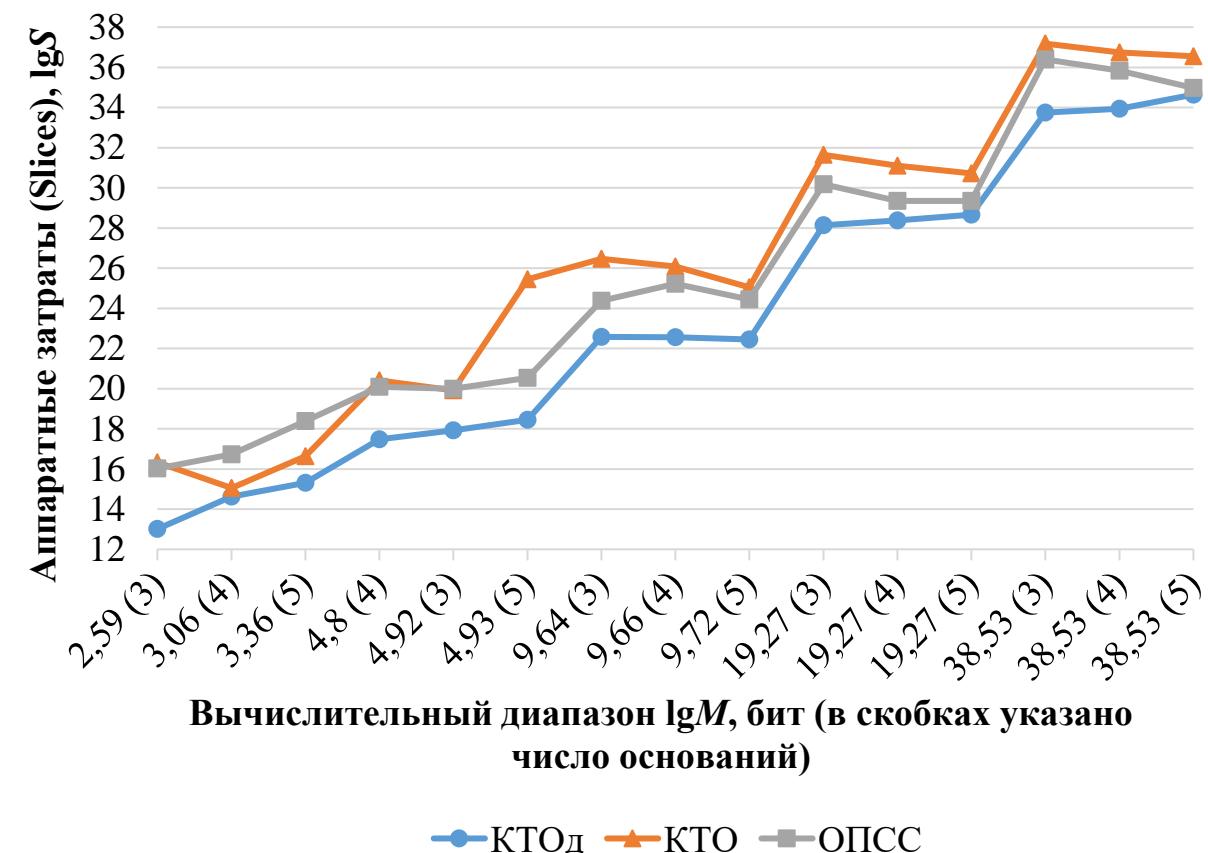

Характеристики устройства коррекции ошибок в СОК с различными диапазонами

| Метод | Разрядность диапазона, бит | Тактовая частота, МГц | Слайсы |

|-------|----------------------------|-----------------------|--------|

| КТОд  | 18                         | 89                    | 100    |

|       | 33                         | 81                    | 220    |

|       | 49                         | 70                    | 440    |

|       | 65                         | 62                    | 689    |

|       | 81                         | 56                    | 1130   |

|       | 97                         | 52                    | 1593   |

| ОПСС  | 18                         | 28                    | 130    |

|       | 33                         | 14                    | 350    |

|       | 49                         | 9                     | 690    |

|       | 65                         | 6                     | 865    |

|       | 81                         | 5                     | 1440   |

|       | 97                         | 4                     | 2330   |

Для анализа характеристик устройства реализации предложенного подхода на программируемых пользователем вентильных матрицах (field-programmable gate array, FPGA) выполнено проектирование на плате Kintex-7 KC705 XC7K70T-2FBG676 без блоков DSP48E1 в среде ISE Design Suite 14.7.

## Основные результаты по положению 3

1. Разработана модифицированная версия КТО для выполнения преобразования остатков в двоичный код. Эффективность представленного подхода достигается за счет упрощения вычислений с дробями. Предложенный метод обратного преобразования чисел из СОК в ПСС на основе дробных величин и архитектура для его реализации существенно проясняют требуемое количество двоичных значений аналогичным избыточные оценкам, что позволяет производить вычисления с использованием минимального требуемого количества обрабатываемых бит. Результаты предварительного моделирования указывают на сокращение ресурсозатрат при реализации рассматриваемой операции для ЦОС.

2. Разработаны метод определения знака числа в СОК, основанный на применении дробных величин. Предложенный выбор точности при вычислении грубой оценки знака позволяет снизить количество обрабатываемых разрядов до величины примерно пропорциональной логарифму диапазона СОК, в то время как лучшие из известных методов имеют время выполнения, линейно зависящее от диапазона. Расчеты показали превосходство по скорости вычислений предложенного метода на основе дробных величин над известными аналогами на основе КТО и ОПСС. Данное обстоятельство имеет место для СОК с произвольным заданным набором модулей. В случае задания СОК со специальным подбором модулей вида  $2^k \pm 1$  возможно создание более быстрых узкоспециализированных решений для определения знака числа. Разработанный метод является универсальным и не привязан к какому-либо набору модулей.

3. Для решения задачи сравнения чисел в СОК разработаны метод и архитектура на основе дробных величин, позволяющие сократить количество используемых операций при реализации параллельной обработки данных в модулярном коде, что указывает на возможность значимого снижения ресурсозатрат при реализации рассматриваемой немодульной операции с использованием различных наборов модулей СОК на базе платформ ППВМ и ИССН для решения различных задач ЦОС.

4. Для решения задач обнаружения, локализации и исправления ошибочного разряда предложены метод и архитектура, последовательность действий при реализации которых способна оптимизировать обработку данных в модулярном коде при локализации ошибочного разряда с помощью дробных величин. Благодаря использованию дробных значений удается заменить сложные операторы преобразования чисел из СОК в ОПСС более простыми операциями сложения, что приводит к значительному снижению ресурсозатрат на обработку цифровых данных, а также к перспективному повышению производительности вычислений при реализации предложенных структур на базе платформ ППВМ и ИССН.

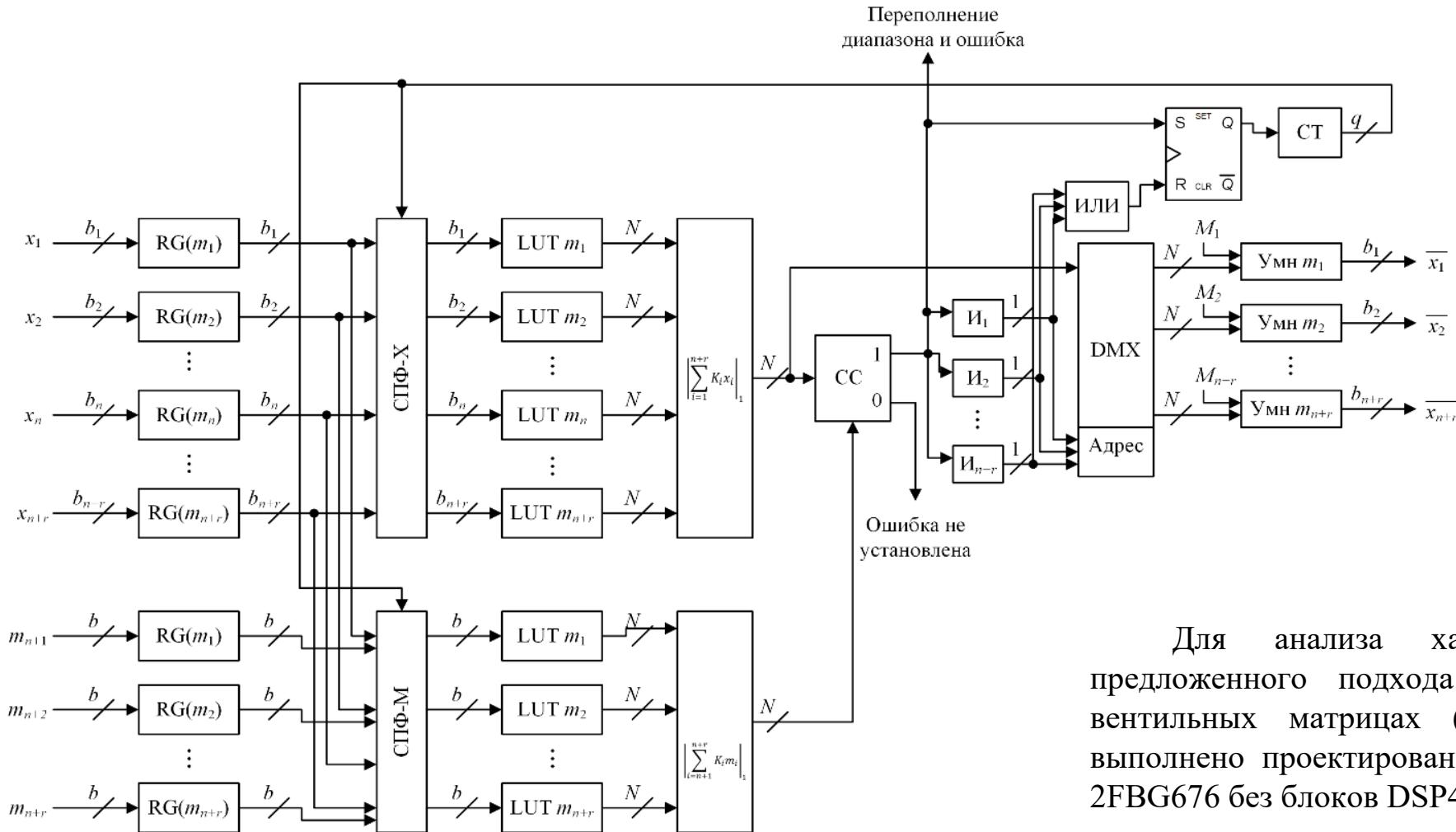

# Двумерная цифровая фильтрация в позиционной системе счисления и в системе остаточных классов с масштабированными коэффициентами

Коэффициенты  $f_{i,j}$  фильтра  $F$  предварительно масштабируются на  $k$  бит и округляются к большему по формуле  $f_{i,j}^* = \lceil 2^k f_{i,j} \rceil$ . Данные коэффициенты хранятся в памяти устройства в виде констант и используются для свертки с исходным изображением по формуле

$$I_2^*(x, y) = \sum_{i=-1}^l \sum_{j=-1}^l I_1(x - i, y - j) \cdot f_{i,j}^*. \text{ После чего выполняется обратное масштабирование результатов свертки по формуле } I_2(x, y) = \lfloor I_2^*(x, y) / 2^k \rfloor.$$

При организации вычислений в СОК все данные необходимо предварительно перевести из ПСС в СОК с набором модулей  $\{m_1, \dots, m_n\}$ . После выполнения свертки по каждому модулю результаты переводятся из СОК в ПСС.

**Положение 5. Метод и алгоритм дискретного вейвлет-преобразования многомерных сигналов с использованием масштабированных коэффициентов и параллельной обработкой в системе остаточных классов, представляющие собой комплексную реализацию обобщенной модели для задач обработки изображений**

## Анализ вычислительной погрешности двумерной цифровой фильтрации с использованием масштабированных коэффициентов (начало)

Погрешность цифровой фильтрации зависит от точности представления его коэффициентов в памяти устройства, то есть от параметра масштабирования  $k$ . Абсолютная погрешность (АП)  $E_1$  масштабирования и округления коэффициентов  $f_{i,j}$  двумерного пространственного фильтра  $F$  размера  $(2l+1) \times (2l+1)$  вычисляется

по формуле  $E_1 = \sum_{i=-l}^l \sum_{j=-1}^l (2^k f_{i,j} - 2^k \bar{f}_{i,j})$ . В случае, когда конкретные значения коэффициентов не известны, либо

подлежат изменению, используется предельная абсолютная погрешность (ПАП)  $E_2$  ( $E_2 \geq E_1$ ) преобразования коэффициентов  $E_2 = (2l+1)^2 - \varepsilon$ , где  $\varepsilon$  – машинный ноль. ПАП  $E_3$  свертки вычисляется из выражения  $E_3 = E_2 \cdot M_{max} = M_{max} (2l+1)^2 - \varepsilon$ . ПАП  $E_4$  масштабированных результатов свертки рассчитывается по формуле

$E_4 = \frac{E_3}{2^k} = 2^{-k} M_{max} (2l+1)^2 - \varepsilon$ . ПАП  $E_5$  округления масштабированных результатов свертки вычисляется из уравнения  $E_5 = E_4 + \beta - \lfloor E_4 + \beta \rfloor$ , где  $\beta$  – дробная часть точного результата свертки. ПАП  $E_6$  округленных

масштабированных результатов свертки рассчитывается по формуле  $E_6 = |E_4 - E_5|$ . Подставив в данную формулу значение  $E_5$ , получим  $E_6 = |E_4 - (E_4 + \beta - \lfloor E_4 + \beta \rfloor)| = |\lfloor E_4 + \beta \rfloor - \beta|$ . Если  $|\lfloor E_4 + \beta \rfloor - \beta| > 0$ , то  $|\lfloor E_4 + \beta \rfloor| \geq 1$ , тогда чем больше значение  $|\lfloor E_4 + \beta \rfloor|$ , тем больше погрешность  $E_6$ . В этом случае  $|\lfloor E_4 + \beta \rfloor| = |\lfloor E_4 \rfloor| + 1$ ,  $\beta = |\lfloor E_4 \rfloor| + 1 - E_4$  и  $E_6 = |\lfloor E_4 + |\lfloor E_4 \rfloor| + 1 - E_4 \rfloor - (|\lfloor E_4 \rfloor| + 1 - E_4)| = E_4$ . Если же  $|\lfloor E_4 + \beta \rfloor| - \beta \leq 0$ , то  $|\lfloor E_4 + \beta \rfloor| \leq \beta$ . Откуда  $E_4 + \beta = 0$  и  $E_6 = |0 - \beta| = \beta$ .

**Положение 5.** Метод и алгоритм дискретного вейвлет-преобразования многомерных сигналов с использованием масштабированных коэффициентов и параллельной обработкой в системе остаточных классов, представляющие собой комплексную реализацию обобщенной модели для задач обработки изображений

## Анализ вычислительной погрешности двумерной цифровой фильтрации с использованием масштабированных коэффициентов (окончание)

Тогда чем больше значение  $\beta$ , тем больше погрешность  $E_6$ . В этом случае  $\lfloor E_4 + \beta \rfloor = 0$ , откуда  $E_4 + \beta = 1 - \varepsilon$  и  $\beta = 1 - E_4 - \varepsilon \leq 1 - \varepsilon$ . Тогда  $E_6 = |0 + 1 - \varepsilon - (1 - \varepsilon)| = |0 - (1 - \varepsilon)| = 1 - \varepsilon$ . Таким образом  $E_6$

вычисляется из выражения  $E_6 = \begin{cases} E_4, & E_4 \geq 1, \\ 1 - \varepsilon, & E_4 < 1. \end{cases}$

Подставив значение  $E_4$ , получим

$$E_6 = \begin{cases} 2^{-k} M_{max} (2l+1)^2 - \varepsilon, & 2^{-k} M_{max} (2l+1)^2 - \varepsilon \geq 1, \\ 1 - \varepsilon, & 2^{-k} M_{max} (2l+1)^2 - \varepsilon < 1; \end{cases} \Rightarrow E_6 = \begin{cases} 2^{-k} M_{max} (2l+1)^2, & 2^k < M_{max} (2l+1)^2, \\ 1, & 2^k \geq M_{max} (2l+1)^2. \end{cases}$$

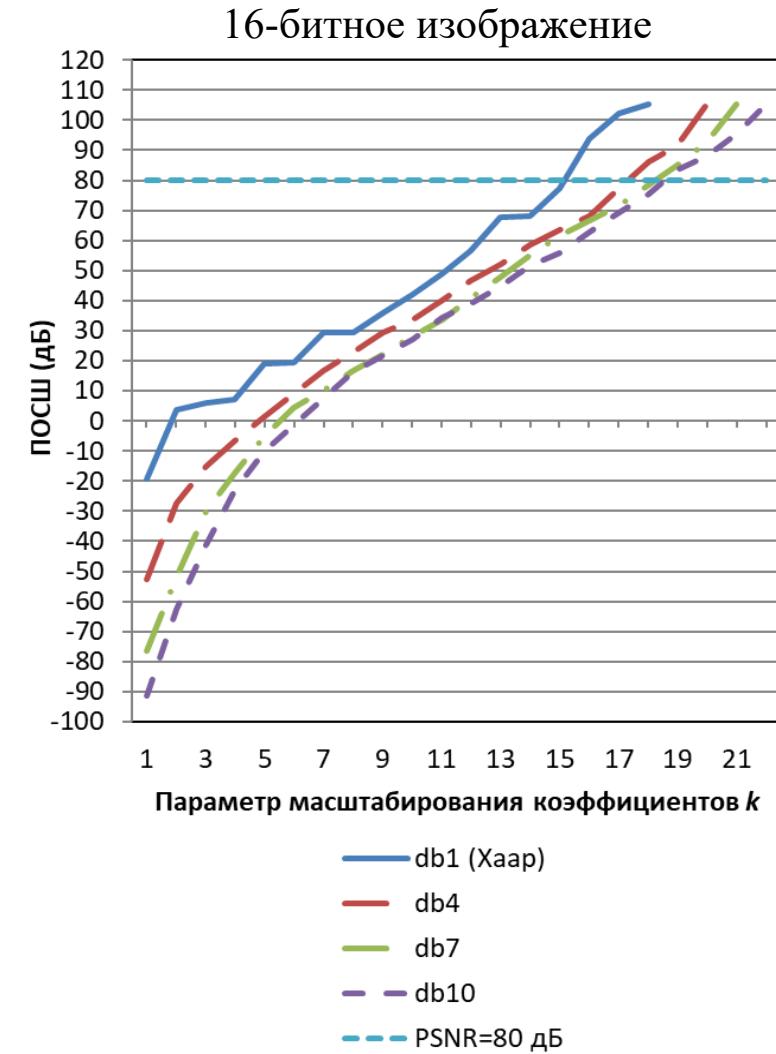

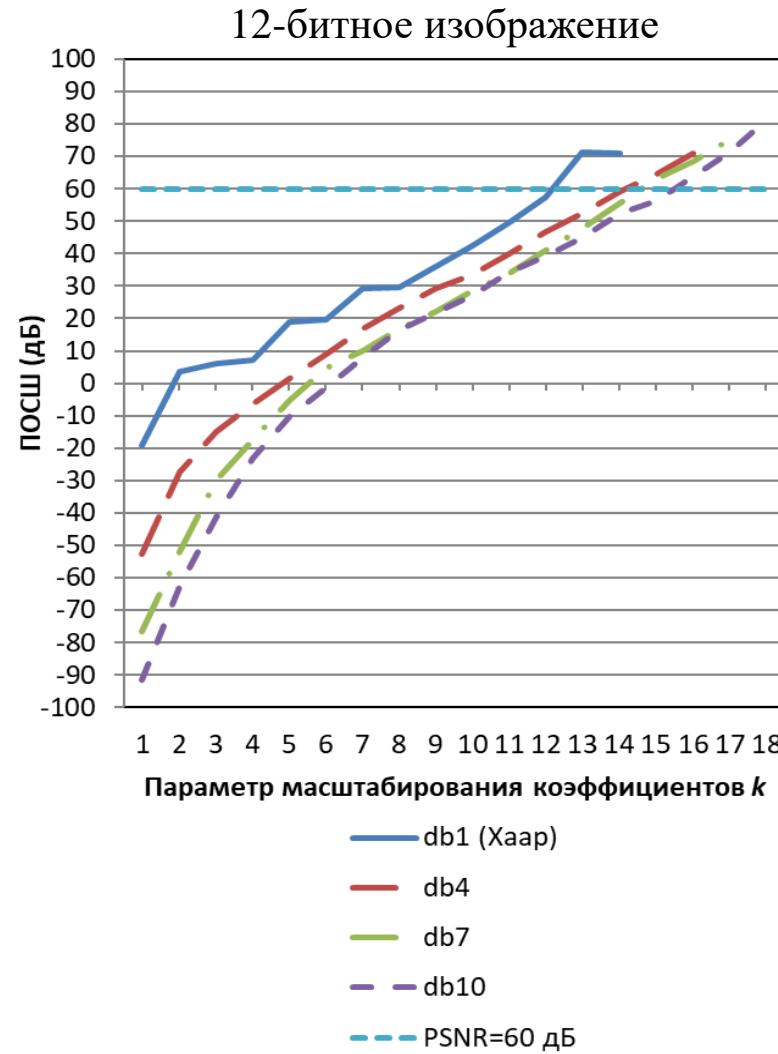

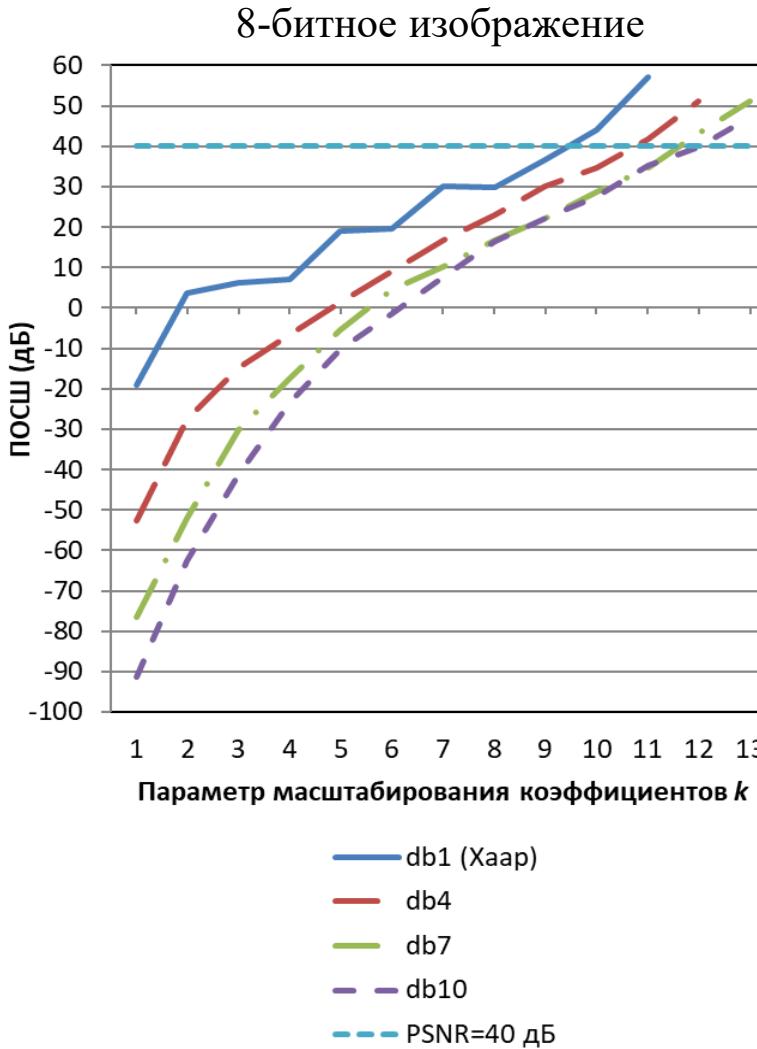

Результирующая погрешность цифровой фильтрации  $MSE \leq E_6^2$ , где  $MSE$  – среднеквадратическое отклонение, и минимальное качество обработки изображения рассчитывается по формуле  $PSNR = 20 \log_{10} (M_{max} / E_6)$ , где  $PSNR$  – пиковое отношение сигнал-шум между исходным и обработанным изображениями, а  $M_{max}$  – максимальное значение яркости пикселей. Подставив полученное выражение  $E_6$ , получим

$$PSNR > \begin{cases} 20 \log_{10} \left( \frac{2^k}{(2l+1)^2} \right), & 2^k < M_{max} (2l+1)^2, \\ 20 \log_{10} M_{max}, & 2^k \geq M_{max} (2l+1)^2. \end{cases}$$

**Положение 5.** Метод и алгоритм дискретного вейвлет-преобразования многомерных сигналов с использованием масштабированных коэффициентов и параллельной обработкой в системе остаточных классов, представляющие собой комплексную реализацию обобщенной модели для задач обработки изображений

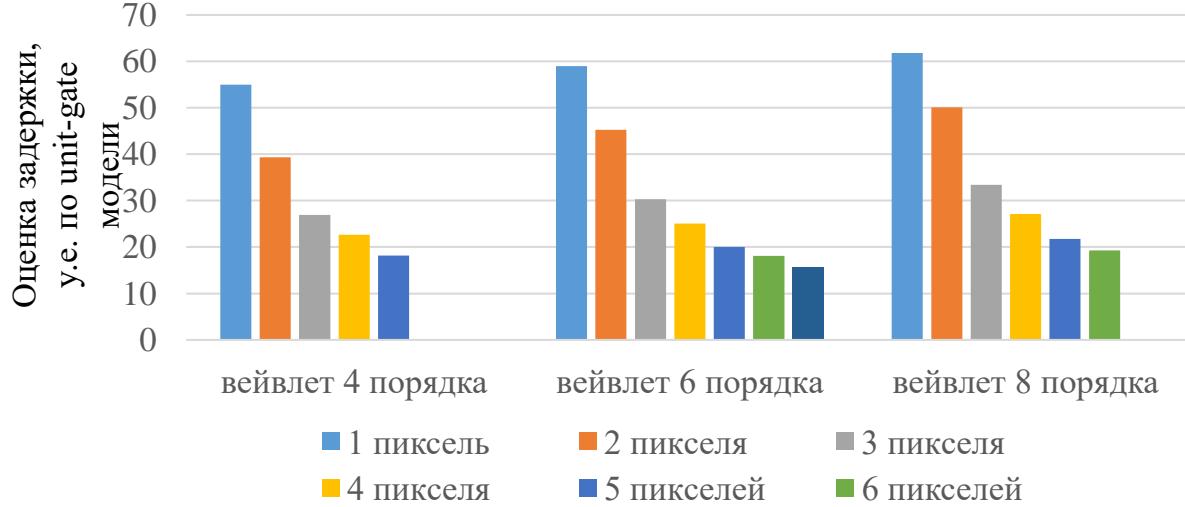

# Анализ вычислительной погрешности вейвлетной обработки изображений с масштабированными коэффициентами (начало)

Коэффициенты  $f_{F,i}$  вейвлет-фильтра  $F$  масштабируются на  $k$  двоичных разрядов и округляются к большему по формуле

$$f_{F,i}^* = \lceil 2^k f_{F,i} \rceil.$$

Далее выполняется вейвлет-обработка изображения  $I$  с использованием масштабированных коэффициентов. Полученный результат  $I^*$  преобразуется по формуле

$$\tilde{I} = \left\lfloor 2^{-4k} I^* \right\rfloor \text{ или } \tilde{I} = \left\lfloor 2^{-6k} I^* \right\rfloor$$

в случае двумерного или трехмерного изображения, соответственно.

**Положение 5.** Метод и алгоритм дискретного вейвлет-преобразования многомерных сигналов с использованием масштабированных коэффициентов и параллельной обработкой в системе остаточных классов, представляющие собой комплексную реализацию обобщенной модели для задач обработки изображений

# Анализ вычислительной погрешности вейвлетной обработки изображений с масштабированными коэффициентами (продолжение)

Этап 1. Масштабирование коэффициентов вейвлет-фильтров.

$$T_1^{[L]} = \sum_{i=1}^l 2^k f_{L,i} = 2^k \sum_{i=1}^l f_{L,i} = 2^k \cdot \sqrt{2} = 2^{k+1/2} = 2^k \sum_{i=1}^l f_{L,i} = 2^k \cdot \sqrt{2} = 2^{k+1/2},$$

где  $T_1^{[L]}$  – точное значение суммы коэффициентов вейвлет-фильтров  $L$ .

$$\begin{aligned} T_1^{[H]} &= \sum_{i=1}^l 2^k f_{L,i} = 2^k \sum_{i=1}^l f_{H,i} = 2^k \cdot 0 = 0, \\ T_{1,1}^{[L]} &= \sum_{i=1}^{\frac{l}{2}} 2^k f_{L,2i-1}, T_{1,1}^{[H]} = \sum_{i=1}^{\frac{l}{2}} 2^k f_{H,2i-1}, \\ T_{1,2}^{[H]} &= \sum_{i=1}^{\frac{l}{2}} 2^k f_{H,2i}, E_1^{[L]} = \sum_{i=1}^l (\lceil 2^k f_{L,i} \rceil - 2^k f_{L,i}). \end{aligned}$$

где  $E_1^{[L]}$  – сумма АП округления коэффициентов фильтра  $L$ .

$$\begin{aligned} E_1^{[H]} &= \sum_{i=1}^l (\lceil 2^k f_{H,i} \rceil - 2^k f_{H,i}), E_{1,1}^{[L]} = \sum_{i=1}^{\frac{l}{2}} (\lceil 2^k f_{L,2i-1} \rceil - 2^k f_{L,2i-1}), E_{1,2}^{[L]} = \sum_{i=1}^{\frac{l}{2}} (\lceil 2^k f_{L,2i} \rceil - 2^k f_{L,2i}), \\ E_{1,1}^{[H]} &= \sum_{i=1}^{\frac{l}{2}} (\lceil 2^k f_{H,2i-1} \rceil - 2^k f_{H,2i-1}), E_{1,2}^{[H]} = \sum_{i=1}^{\frac{l}{2}} (\lceil 2^k f_{H,2i} \rceil - 2^k f_{H,2i}). \end{aligned}$$

Этап 2. Свертка по строкам (анализ).

$$T_2^{[L]} = T_1^{[L]} \cdot M_{max},$$

где:  $T_2^{[L]}$  – точное значение вычислений на этапе 2, полученное после обработки изображения фильтром  $L$ ;  $M_{max}$  – максимальное значение яркости пикселей обрабатываемого изображения.

**Положение 5. Метод и алгоритм дискретного вейвлет-преобразования многомерных сигналов с использованием масштабированных коэффициентов и параллельной обработкой в системе остаточных классов, представляющие собой комплексную реализацию обобщенной модели для задач обработки изображений**

# Анализ вычислительной погрешности вейвлетной обработки изображений с масштабированными коэффициентами (продолжение)

$$E_2^{[L]} = E_1^{[L]} \cdot M_{max},$$

где  $E_2^{[L]}$  – ПАП вычислений на этапе 2, полученная после обработки изображения фильтром  $L$ .

$$E_2^{[H]} = E_1^{[H]} \cdot M_{max}.$$

Здесь и далее все  $T_j^{[F]} = 0$  ( $j > 1$ ), где  $F$  – последовательность фильтров обработки изображения, содержащая  $H$ , так как  $T_1^{[H]} = 0$ .

Этап 3. Свертка по столбцам (анализ).

$$T_3^{[LL]} = T_2^{[LL]} \cdot T_1^{[L]},$$

где  $T_3^{[LL]}$  – точное значение вычислений на этапе 3, полученное после двукратной последовательной обработки изображения фильтром  $L$ .

$$E_3^{[LL]} = (T_2^{[L]} + E_2^{[L]})(T_1^{[L]} + E_1^{[L]}) - T_3^{[LL]},$$

где  $E_3^{[LL]}$  – ПАП вычислений на этапе 3, полученная после двукратной последовательной обработки изображения фильтром  $L$ .

$$E_3^{[LH]} = (T_2^{[L]} + E_2^{[L]})E_1^{[H]}, E_3^{[HL]} = E_2^{[H]}(T_1^{[L]} + E_1^{[L]}), E_3^{[HH]} = E_2^{[H]} \cdot E_1^{[H]}.$$

Этап 4. Свертка по столбцам (синтез).

$$T_{4,\lambda}^{[LLL]} = T_3^{[LL]} \cdot T_{1,\lambda}^{[L]}, E_{4,\lambda}^{[LLL]} = (T_3^{[LL]} + E_3^{[LL]})(T_{1,\lambda}^{[L]} + E_{1,\lambda}^{[L]}) - T_{4,\lambda}^{[LLL]}, E_{4,\lambda}^{[LHH]} = E_3^{[LH]}(T_{1,\lambda}^{[H]} + E_{1,\lambda}^{[H]}), E_{4,\lambda}^{[HLL]} = E_3^{[HL]}(T_{1,\lambda}^{[L]} + E_{1,\lambda}^{[L]}), E_{4,\lambda}^{[HHH]} = E_3^{[HH]}(T_{1,\lambda}^{[H]} + E_{1,\lambda}^{[H]}).$$

Этап 5. Суммирование по столбцам.

$$E_{5,\lambda}^{[L]} = E_{4,\lambda}^{[LLL]} + E_{4,\lambda}^{[LHH]}, E_{5,\lambda}^{[H]} = E_{4,\lambda}^{[HLL]} + E_{4,\lambda}^{[HHH]}.$$

**Положение 5. Метод и алгоритм дискретного вейвлет-преобразования многомерных сигналов с использованием масштабированных коэффициентов и параллельной обработкой в системе остаточных классов, представляющие собой комплексную реализацию обобщенной модели для задач обработки изображений**

# Анализ вычислительной погрешности вейвлетной обработки изображений с масштабированными коэффициентами (окончание)

## Этап 6. Свертка по строкам (синтез).

$$\begin{aligned} T_{6,1}^{[L]} &= T_{4,1}^{[LLL]} \cdot T_1^{[L]}, T_{6,2}^{[L]} = T_{4,2}^{[LLL]} \cdot T_1^{[L]}, T_{6,3}^{[L]} = T_{4,1}^{[LLL]} \cdot T_2^{[L]}, T_{6,4}^{[L]} = T_{4,2}^{[LLL]} \cdot T_2^{[L]}, E_{6,1}^{[L]} = (T_{4,1}^{[LLL]} + E_{5,1}^{[L]}) (T_{1,1}^{[L]} + E_{1,1}^{[L]}) - T_{6,1}^{[L]}, E_{6,2}^{[L]} = (T_{4,2}^{[LLL]} + E_{5,2}^{[L]}) (T_{1,1}^{[L]} + E_{1,1}^{[L]}) - T_{6,2}^{[L]}, \\ E_{6,3}^{[L]} &= (T_{4,1}^{[LLL]} + E_{5,1}^{[L]}) (T_{1,2}^{[L]} + E_{1,2}^{[L]}) - T_{6,3}^{[L]}, E_{6,4}^{[L]} = (T_{4,2}^{[LLL]} + E_{5,2}^{[L]}) (T_{1,2}^{[L]} + E_{1,2}^{[L]}) - T_{6,4}^{[L]}, E_{6,1}^{[H]} = E_{5,1}^{[H]} (T_{1,1}^{[H]} + E_{1,1}^{[H]}), E_{6,2}^{[H]} = E_{5,2}^{[H]} (T_{1,1}^{[H]} + E_{1,1}^{[H]}), \\ E_{6,3}^{[H]} &= E_{5,1}^{[H]} (T_{1,2}^{[H]} + E_{1,2}^{[H]}), E_{6,4}^{[H]} = E_{5,2}^{[H]} (T_{1,2}^{[H]} + E_{1,2}^{[H]}). \end{aligned}$$

## Этап 7. Суммирование по строкам.

$$E_{7,\lambda} = E_{6,\lambda}^{[L]} + E_{6,\lambda}^{[H]}.$$

## Этап 8. Масштабирование результатов вычислений.

$$E_{8,\lambda} = \left\lfloor 2^{-4k} E_{7,\lambda} \right\rfloor.$$

Значения  $E_{8,\lambda}$  ( $\lambda = \overline{1,4}$ ) – это максимальная результирующая погрешность ВО двумерных изображений с использованием масштабированных коэффициентов ВФ, позволяющая вычислить среднеквадратическое отклонение  $MSE$  по формуле

$$MSE = 2^{-2} \sum_{\lambda=1}^4 E_{8,\lambda}^2$$

и минимально возможное качество вейвлет-обработки изображения

$$PSNR = 20 \log_{10} \left( 2^2 M_{max} / \sum_{\lambda=1}^4 E_{8,\lambda}^2 \right).$$

Разрядность  $r_{f_{F,i}^*}$  масштабированных коэффициентов  $f_{F,i}^*$  вейвлет-фильтров вычисляется по формуле

$$r_{f_{F,i}^*} = \left\lceil \log_2 (|f_{F,i}^*| + 1) \right\rceil + 1.$$

**Положение 5. Метод и алгоритм дискретного вейвлет-преобразования многомерных сигналов с использованием масштабированных коэффициентов и параллельной обработкой в системе остаточных классов, представляющие собой комплексную реализацию обобщенной модели для задач обработки изображений**

# Теоретическая оценка наихудшего возможного качества вейвлет-обработки трехмерных полутоновых изображений с масштабированными коэффициентами

**Положение 5.** Метод и алгоритм дискретного вейвлет-преобразования многомерных сигналов с использованием масштабированных коэффициентов и параллельной обработкой в системе остаточных классов, представляющие собой комплексную реализацию обобщенной модели для задач обработки изображений

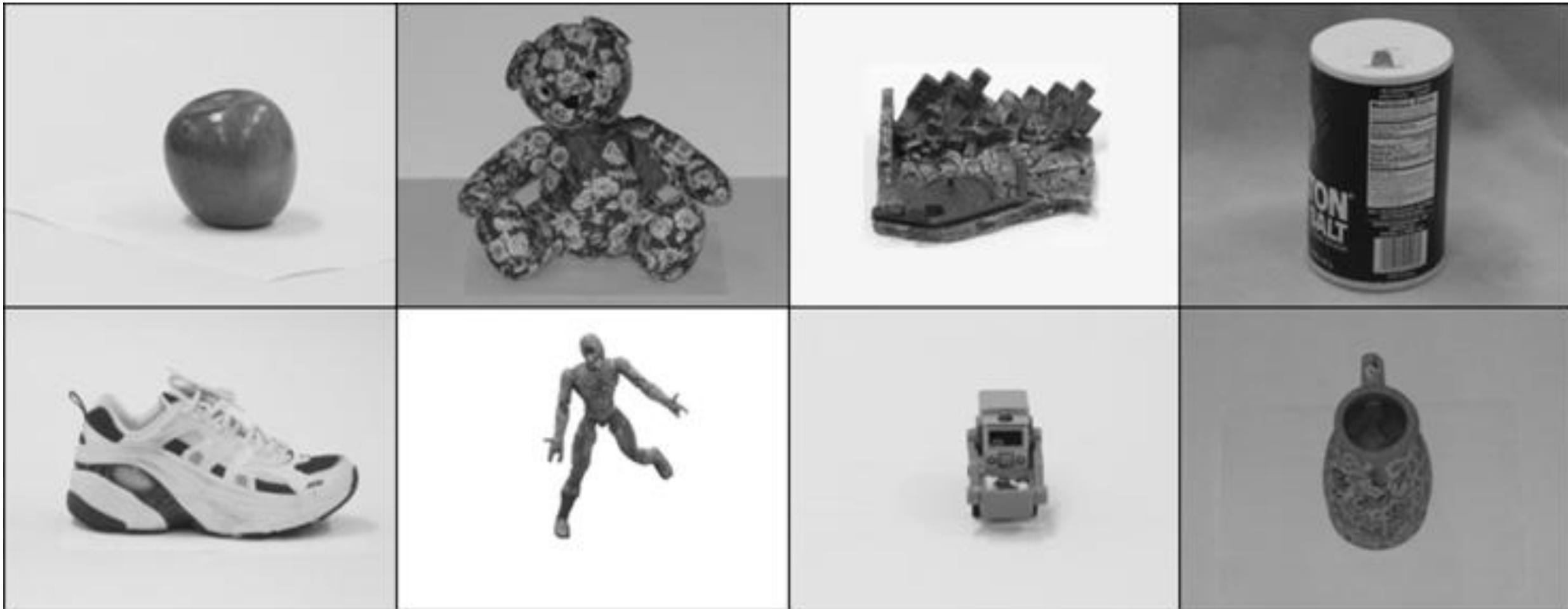

# Пример программной вейвлет-обработки трехмерной компьютерной томограммы околоносовых пазух (120-ый кадр) вейвлетом Добеши 14 порядка (MATLAB)

Исходный кадр

томограммы

Результат выполнения

прямого и обратного

дискретного вейвлет-

преобразования с

использованием 9-битных

коэффициентов,

ПОСШ=35,7 дБ

Результат выполнения

прямого и обратного

дискретного вейвлет-

преобразования с

использованием 5-битных

коэффициентов,

ПОСШ=18,2 дБ

Результат выполнения

прямого и обратного

дискретного вейвлет-

преобразования с

использованием 13-битных

коэффициентов,

ПОСШ=62,1 дБ

Положение 5. Метод и алгоритм дискретного вейвлет-преобразования многомерных сигналов с использованием масштабированных коэффициентов и параллельной обработкой в системе остаточных классов, представляющие собой комплексную реализацию обобщенной модели для задач обработки изображений

## **Основные результаты по положению 4**

1. В результате рассмотрения подходов к цифровой фильтрации двумерных сигналов с параллельной организацией вычислений в СОК и использованием масштабированных коэффициентов ЦФ для уменьшения вычислительной сложности и снижения задержки методов ЦОС установлено, что реализация цифровой фильтрации сигналов в формате с фиксированной точкой открывает возможность проектирования высокопроизводительных аппаратных структур на базе современных платформ ППВМ и ИССН. Параметр масштабирования множитель позволяет значительно упростить и ускорить операции с его использованием при сохранении высокого качества обработки сигналов в терминах ПОСШ.

2. Предложен алгоритм масштабирования коэффициентов ВФ для обработки сигналов в СОК, учитывающий накопительную погрешность многократной последовательной свертки с анализирующими и синтезирующими ВФ при прямом и обратном ДВП данных и гарантирующий достижение высокого качества восстанавливаемого сигнала в терминах ПОСШ. Данный алгоритм позволяет выполнить предварительное преобразование коэффициентов ВФ, используемых для ВО многомерных сигналов.

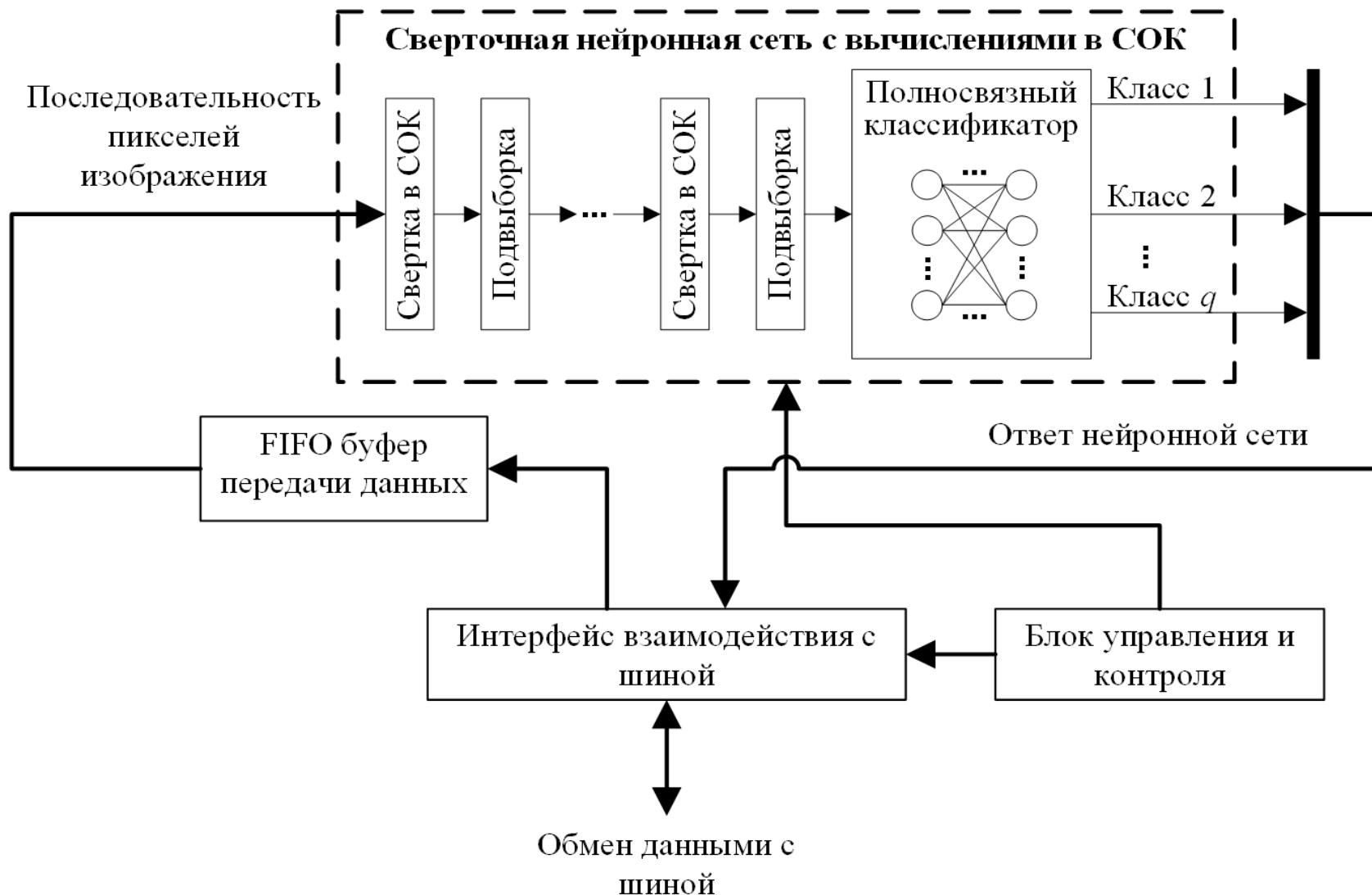

3. Разработан метод вейвлет-фильтрации цифровых сигналов с параллельной организацией вычислений в СОК, использующий масштабированные коэффициенты ВФ для снижения вычислительной сложности блоков цифровой фильтрации и улучшения эксплуатационных показателей систем ЦОС. Распараллеливание вычислений в СОК на арифметико-логическом уровне при проектировании устройств ВО многомерных сигналов позволяет распределить вычислительную нагрузку по нескольким каналам, снижая задержку блоков цифровой вейвлет-фильтрации.

4. На основе проведенного программного моделирования разработанных метода и алгоритма вейвлет-фильтрации многомерных сигналов с использованием трехмерных медицинских томограмм выявлено, что чрезмерное масштабирование приводит к возникновению равномерно распределенных видимых искажений при ВО визуальных данных.

**Положение 5. Метод и алгоритм дискретного вейвлет-преобразования многомерных сигналов с использованием масштабированных коэффициентов и параллельной обработкой в системе остаточных классов, представляющие собой комплексную реализацию обобщенной модели для задач обработки изображений**

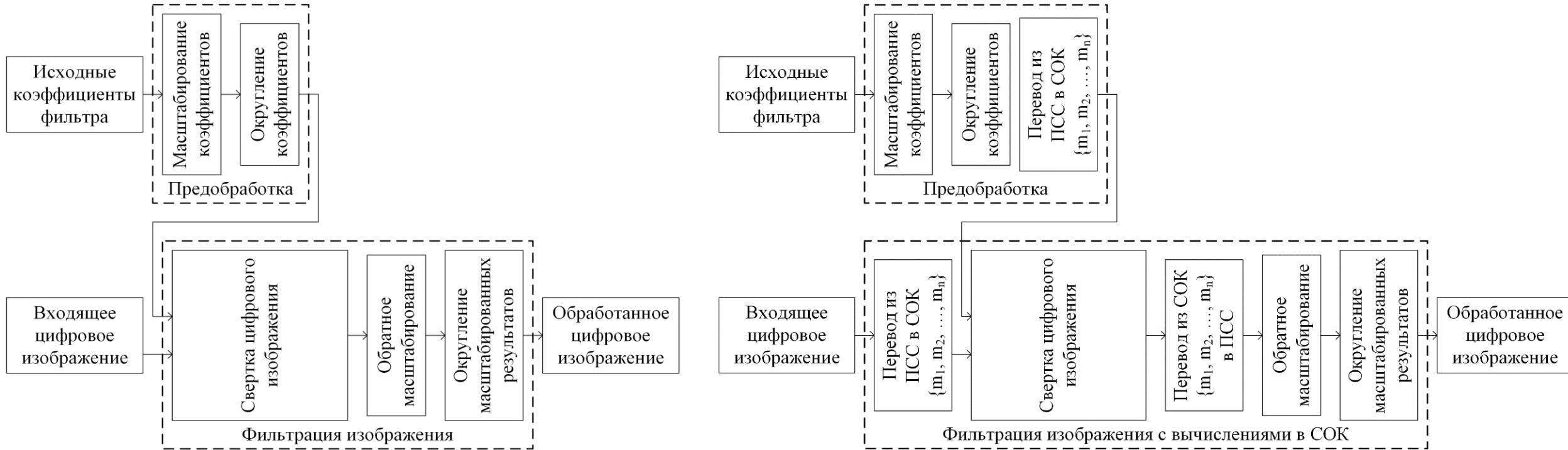

# Схема разработанной технологии

**Положение 6. Технология создания программно-аппаратных систем для высокопроизводительной цифровой обработки сигналов с вычислениями в системе остаточных классов с модулями специального вида на основе дробных величин, представляющая собой практическое воплощение обобщенной модели**

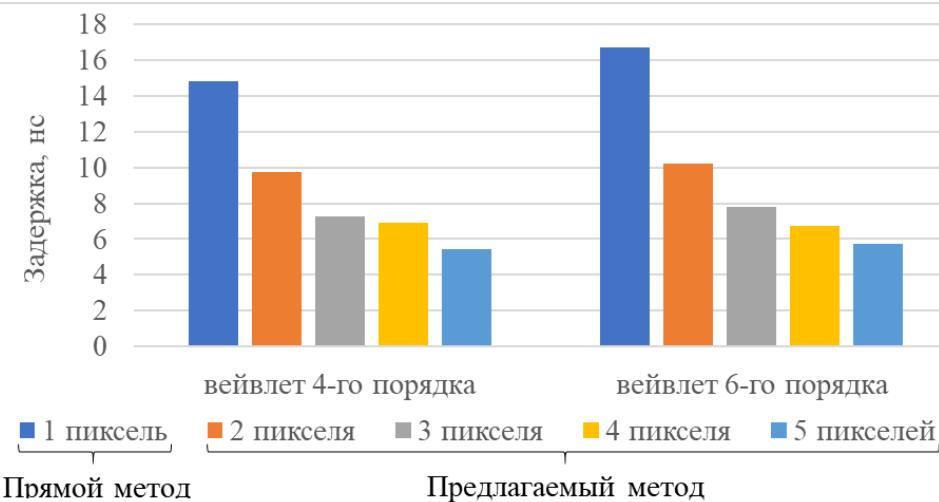

# Результаты аппаратной реализации ЦФ с ТМАС в ПСС и СОК (FPGA, Artix 7)

Результаты по КИХ-ЦФ с  $k=16$

|                           | $k$ | Система счисления |          |           |       |

|---------------------------|-----|-------------------|----------|-----------|-------|

|                           |     | СОК               |          |           | ПСС   |

|                           |     | 3 модуля          | 4 модуля | 5 модулей |       |

| Максимальная частота, МГц | 16  | 278               | 285      | 283       | 139   |

|                           | 32  | 145               | 200      | 212       | 71    |

|                           | 64  | 71                | 90       | 123       | 29    |

| Количество LUT            | 16  | 638               | 588      | 740       | 801   |

|                           | 32  | 1644              | 1603     | 1388      | 2637  |

|                           | 64  | 4162              | 3348     | 3767      | 9645  |

| Энергопотребление, Вт     | 16  | 0,335             | 0,353    | 0,413     | 0,315 |

|                           | 32  | 0,390             | 0,441    | 0,425     | 0,396 |

|                           | 64  | 0,464             | 0,445    | 0,560     | 0,376 |

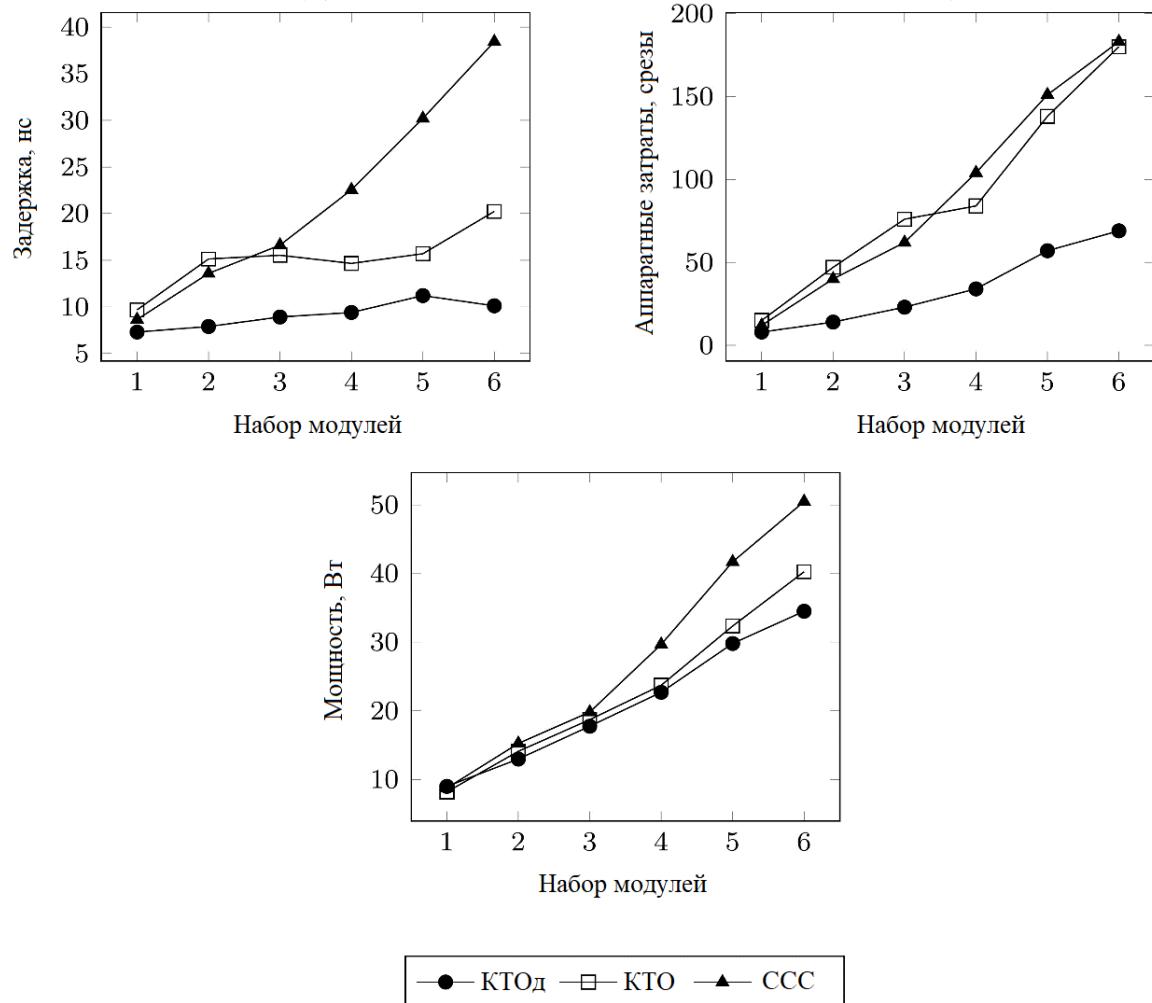

Применение СОК с тремя модулями позволяет увеличить частоту КИХ-ЦФ с  $k=16$  в 1,9-2,2 раз и сократить аппаратные затраты на его реализацию на 10%-44%, при увеличении энергопотребления на 6%-17%. СОК с четырьмя модулями позволяет увеличить частоту КИХ-ЦФ с  $k=16$  в 2-2,4 раз и сократить аппаратные затраты на его реализацию на 15%-55% раз, при увеличении энергопотребления на 3%-23%. СОК с пятью модулями позволяет увеличить частоту КИХ-ЦФ с  $k=16$  примерно в 2 раза и сократить аппаратные затраты на его реализацию на 1%-40%, при увеличении энергопотребления на 0,3%-31%.

Результаты по КИХ-ЦФ 15-го порядка

| К  | Максимальная частота, МГц | Система счисления |          |           | ПСС   |  |

|----|---------------------------|-------------------|----------|-----------|-------|--|

|    |                           | СОК               |          |           |       |  |

|    |                           | 3 модуля          | 4 модуля | 5 модулей |       |  |

| 15 | 295                       | 315               | 310      | 149       | 149   |  |

|    | 292                       | 315               | 305      | 132       | 132   |  |

|    | 278                       | 285               | 283      | 139       | 139   |  |

| 31 | 258                       | 279               | 266      | 135       | 135   |  |

|    | 241                       | 193               | 261      | 433       | 433   |  |

|    | 371                       | 332               | 422      | 426       | 426   |  |

| 31 | 638                       | 588               | 740      | 801       | 801   |  |

|    | 1157                      | 1097              | 1382     | 1283      | 1283  |  |

|    | 0,372                     | 0,323             | 0,338    | 0,337     | 0,337 |  |

| 7  | 371                       | 332               | 422      | 426       | 426   |  |

|    | 638                       | 588               | 740      | 801       | 801   |  |

|    | 0,386                     | 0,340             | 0,377    | 0,331     | 0,331 |  |

| 15 | 0,335                     | 0,353             | 0,413    | 0,413     | 0,315 |  |

|    | 0,433                     | 0,456             | 0,469    | 0,372     | 0,372 |  |

|    | 0,335                     | 0,353             | 0,413    | 0,413     | 0,315 |  |

Применение СОК с тремя модулями позволяет увеличить частоту КИХ-ЦФ 15-го порядка в 2,0-2,5 раз и аппаратные затраты на его реализацию в 1,3-2,3 раз, при увеличении энергопотребления на 6%-19%. СОК с четырьмя модулями позволяет увеличить частоту КИХ-ЦФ 15-го порядка в 2,1-3,1 раз и аппаратные затраты на его реализацию в 1,4-2,9 раза, при увеличении энергопотребления на 11%-16%. СОК с пятью модулями позволяет увеличить частоту КИХ-ЦФ 15-го порядка в 2,0-4,2 раз и аппаратные затраты на его реализацию в 1,1-2,6 раз, при увеличении энергопотребления на 7%-33%.

**Положение 6. Технология создания программно-аппаратных систем для высокопроизводительной цифровой обработки сигналов с вычислениями в системе остаточных классов с модулями специального вида на основе дробных величин, представляющая собой практическое воплощение обобщенной модели**

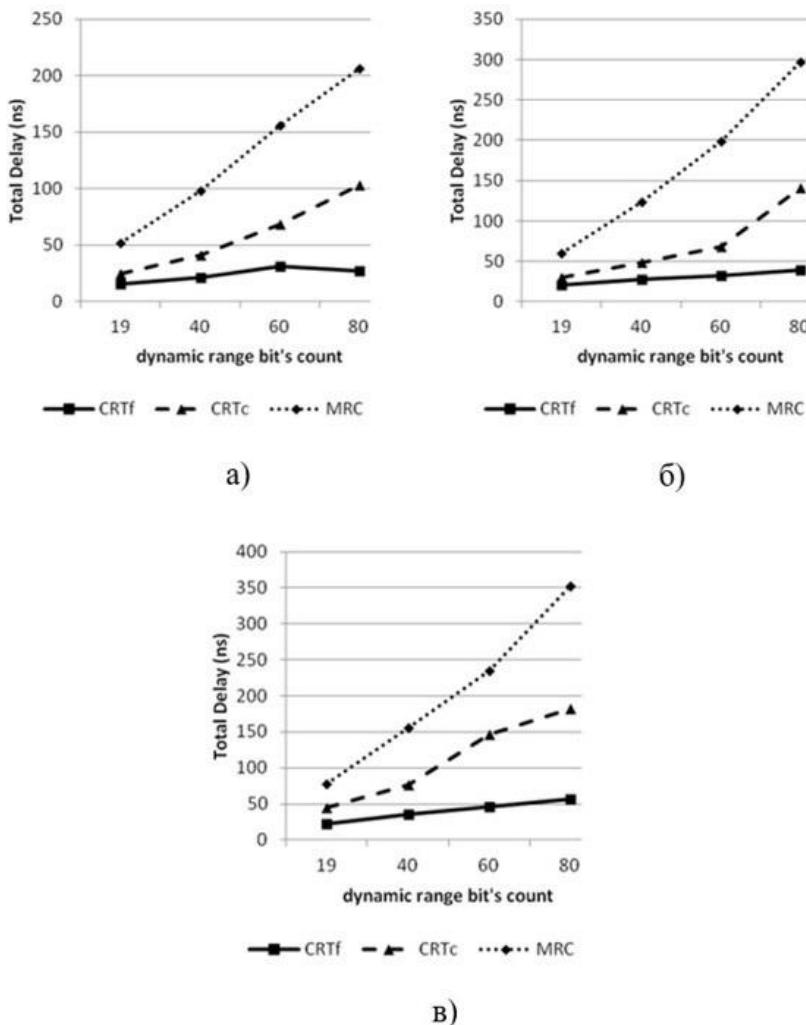

# Результаты реализации МЦФ со сбалансированным набором модулей (ASIC)

Результаты по 32-разрядным диапазонам СОК показали, что предложенный МЦФ эффективнее по аппаратным затратам, чем KSA-фильтр на 21,5%-23% и CPA-фильтр на 20,6%-22,2%. По задержке предложенный метод уступает KSA-фильтру на 48,6%-131,7% и CPA-фильтру на 25,2%-96,9%. По энергопотреблению предложенный МЦФ показал результаты ниже, чем у KSA-фильтра и CPA-фильтра на 21,4%-22,3%. Результаты для 48-разрядных диапазонов СОК показали, что по аппаратным затратам предложенный МЦФ уступил только CPA-фильтру 3 порядка на 1,1%, а в остальных случаях выиграл до 14,3%. По задержке предложенный МЦФ уступает известным до 167,6%.

## Результаты по 32-разрядным диапазонам СОК

| Набор модулей |                           | 7, 15, 16, 31, 127, 2047 на основе сумматоров KSA | 7, 15, 16, 31, 127, 2047 на основе сумматоров CPA | 7, 9, 17, 31, 32, 65, 127 (предложенный) |

|---------------|---------------------------|---------------------------------------------------|---------------------------------------------------|------------------------------------------|

| 3-й порядок   | Площадь, мкм <sup>2</sup> | 20724,69                                          | 20346,38                                          | <b>16139,30</b>                          |

|               | Задержка, нс              | <b>2,37</b>                                       | 3,49                                              | 4,37                                     |

|               | Мощность, мВт             | 9,90                                              | 9,88                                              | <b>7,78</b>                              |

|               | Площадь×задержка          | <b>49117,51</b>                                   | 71008,86                                          | 70528,74                                 |

| 7-ой порядок  | Площадь, мкм <sup>2</sup> | 40456,07                                          | 40074,16                                          | <b>31152,99</b>                          |

|               | Задержка, нс              | <b>3,62</b>                                       | 4,71                                              | 7,79                                     |

|               | Мощность, мВт             | 19,28                                             | 19,25                                             | <b>15,03</b>                             |

|               | Площадь×задержка          | <b>146450,98</b>                                  | 188749,30                                         | 242681,82                                |

| 15-ый порядок | Площадь, мкм <sup>2</sup> | 79856,12                                          | 79465,79                                          | <b>62507,06</b>                          |

|               | Задержка, нс              | <b>6,27</b>                                       | 7,38                                              | 14,53                                    |

|               | Мощность, мВт             | 38,00                                             | 37,98                                             | <b>29,52</b>                             |

|               | Площадь×задержка          | <b>500697,86</b>                                  | 586457,51                                         | 908227,53                                |

| 31-ый порядок | Площадь, мкм <sup>2</sup> | 161175,75                                         | 160775,37                                         | <b>126564,46</b>                         |

|               | Задержка, нс              | <b>18,77</b>                                      | 22,23                                             | 27,89                                    |

|               | Мощность, мВт             | 75,38                                             | 75,36                                             | <b>58,57</b>                             |